# The Intel<sup>®</sup> Microprocessor Family: Hardware and Software Principles and Applications

James L. Antonakos

## THE INTEL MICROPROCESSOR FAMILY

### THE INTEL MICROPROCESSOR FAMILY

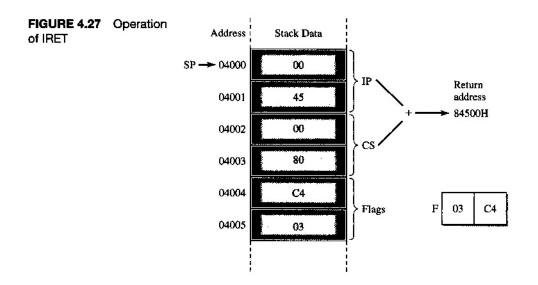

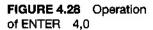

# Hardware and Software Principles and Applications

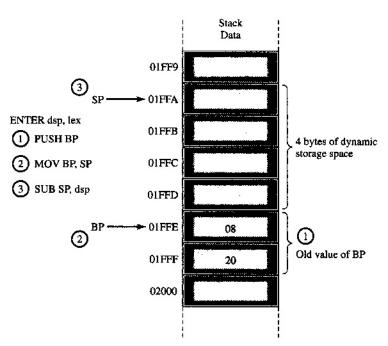

JAMES L. ANTONAKOS

Broome Community College

O Jerome Valencia

Musen selly Engr. Niño E. Merencilla 3/11/047

### **PREFACE**

The rapid advancement of microprocessors into our everyday affairs has both simplified and complicated our lives. Whether we use a computer in our everyday job, or come in contact with one elsewhere, most of us have used a computer at one time or another. Most people know that a microprocessor is lurking somewhere inside the machinery, but what a microprocessor is, and what it does, remains a mystery.

#### PURPOSES OF THE BOOK

This book is intended to help remove the mystery concerning the Intel 80x86 micro-processor family through detailed coverage of its hardware and software and examples of many different applications. Some of the more elaborate applications are visible to us. A large collection of personal computers use 80x86-based architecture, as do some popular commercial video games, electronic engravers, and speech recognition systems. Industry and the government have adopted the 80x86 for many commercial and military applications as well.

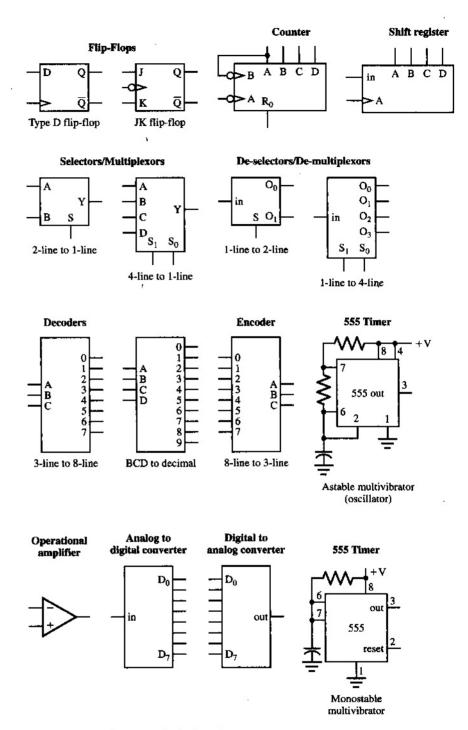

The book is intended for 2- or 4-year electrical engineering, engineering technology, and computer science students. Professional people, such as engineers and technicians, will also find it a handy reference. The material is intended for a one-semester course in microprocessors. Prior knowledge of digital electronics, including combinational and sequential logic, decoders, memories, Boolean algebra, and operations on binary numbers, is helpful. This presumes knowledge of standard computer-related terms, such as RAM, EPROM, TTL, and so forth. Appendix B is included as a reference on binary numbers, and arithmetic and logic functions for those students who would like a quick review.

#### FROM THE 8088 UP

Keep in mind that many of the concepts developed for the 8088 apply to the entire 80x86\* family (via real-mode on the advanced processors). It is not the intention of this book to show the reader how to design a 512 MB motherboard for a Pentium III CPU or write protected-mode assembly language code. Instead, the theory and details of hardware interfacing are presented, along with design techniques, for the 8088 and 8086 CPUs, with the techniques easily extended to more advanced designs. For example, when designing a memory address decoder, the same decoding methods that work with 256 MB memory systems also work with smaller 512 KB memory systems. Because real-mode is available on every Intel 80x86 processor, the majority of the book is spent covering assembly language and software applications.

The 8088 and 8086 CPUs are still widely available as 40-pin DIPs (and even as FPGA software cores for programmable devices) and there continue to be existing and new applications that can be handled by these processors, without the need for the power and speed of the more advanced 32-bit architectures. The 16-bit 8088-based single-board computer system presented in Chapter 12 is still a challenging exercise for the students and a lot easier to construct than any 32-bit 386, 486, or Pentium system could be.

#### **OUTLINE OF COVERAGE**

For those individuals who have no prior knowledge of microprocessors, Chapter 1, Microprocessor-Based Systems, is a good introduction to the microprocessor, how it functions internally, and how it is used in a small system. Chapter 1 is a study of the overall operation of a microprocessor-based system.

Chapter 2, An Introduction to the 80x86 Microprocessor Family, highlights the main features of the 80x86. Data types, addressing modes, and instructions are surveyed. All processors in the 80x86 family are examined as well.

Chapter 3, 80x86 Instructions, Part 1, and Chapter 4, 80x86 Instructions, Part 2, introduce the entire real-mode instruction set of the 80x86. These instructions include data transfer, string, arithmetic, logical, bit manipulation, program transfer, and processor control instructions. Addressing modes, flags, and the structure of a source file are also covered. Over ninety examples are provided to help the student grasp the material. These two chapters are not intended to be read from beginning to end, but instead given a detailed scan. When new instructions are encountered in examples, Chapters 3 and 4 should be consulted, and the sections containing the new instructions read carefully.

Chapter 5, Interrupt Processing, covers the basic sequence of an interrupt, as well as multiple interrupts, special interrupts, and interrupt service routines. The instructor may choose to cover this chapter after Chapter 6 to get right to the programming examples.

\*The term "80x86" is used throughout the text to refer to the entire family of compatible Intel processors, the 8088, 8086, 80286, 80386, 80486, and all the Pentium's. Please think of "80x86" as a single machine as well, one processor having many capabilities.

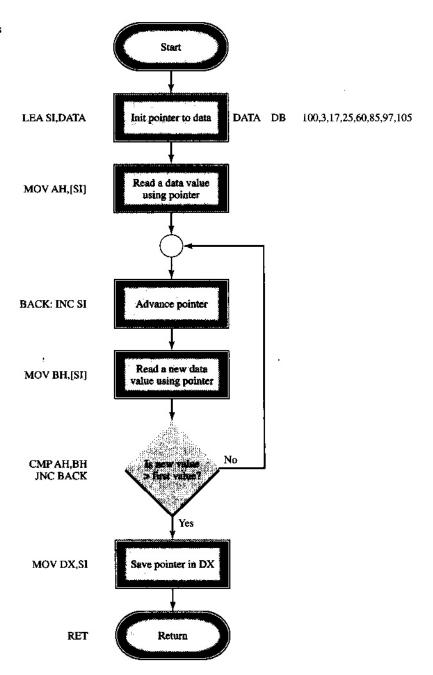

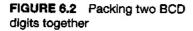

Chapter 6, An Introduction to Programming the 80x86, contains the first real programming efforts. Numerous programming examples show how the 80x86 performs routine functions involving binary and BCD mathematics, string operations, data-table manipulation, and number conversions.

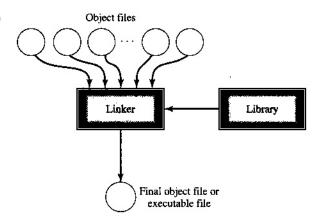

Chapter 7, Advanced Programming Applications, introduces the student to many advanced concepts, such as linking multiple object files, instruction execution time, interrupt handling, memory management, math coprocessor programming, and macro usage. Assembly language in the Windows and Linux environment is also examined. Fifteen more programming applications are included to support the new concepts.

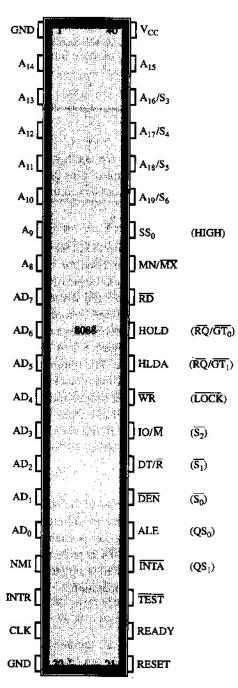

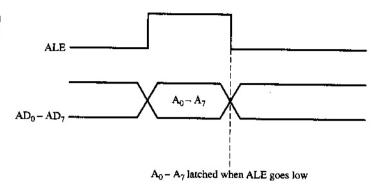

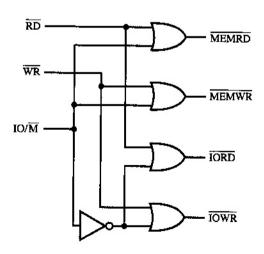

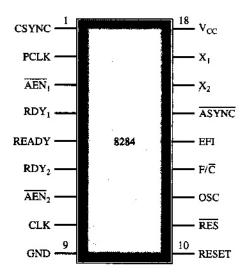

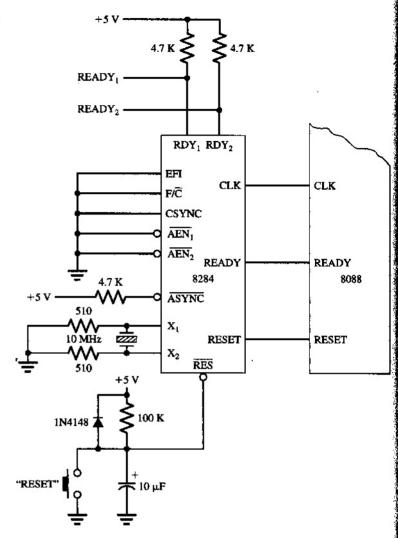

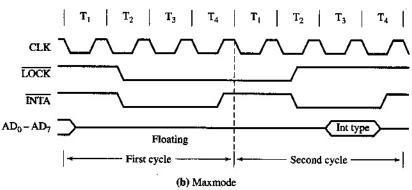

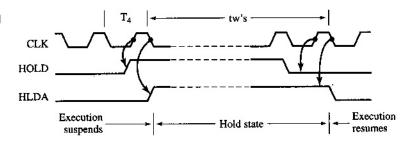

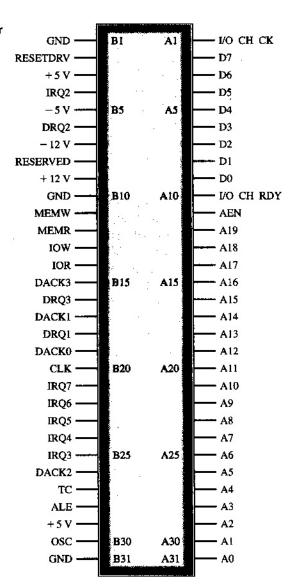

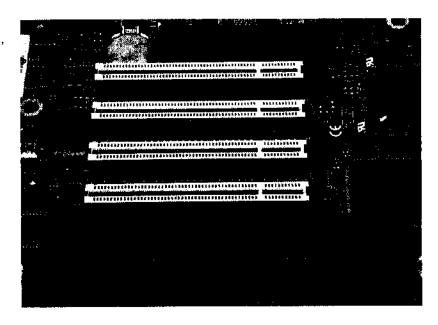

The hardware operation of the 8088 is covered in **Chapter 8, Hardware Details of the 8088.** All CPU pins are discussed, as are timing diagrams, the difference between min-mode and maxmode operation, the Personal Computer Bus Standards, and two chips that are essential to 8088-based systems: the 8284 clock generator and the 8288 bus controller.

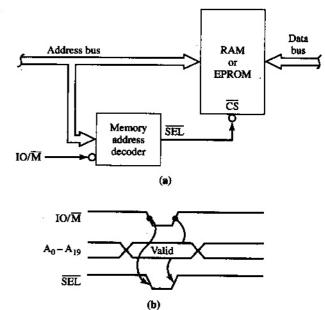

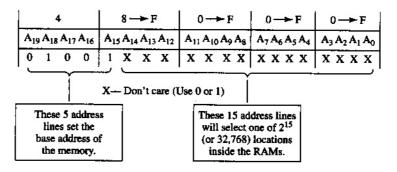

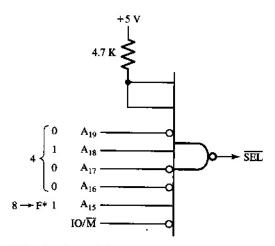

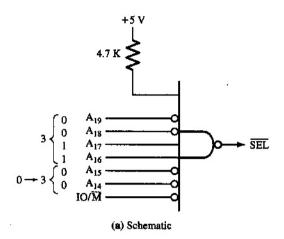

Chapter 9, Memory System Design, covers the details needed to design an operational RAM and EPROM-based memory system for the 8088. Static and dynamic RAMs, EPROMs, DMA, and full and partial address decoding are covered.

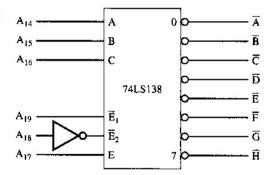

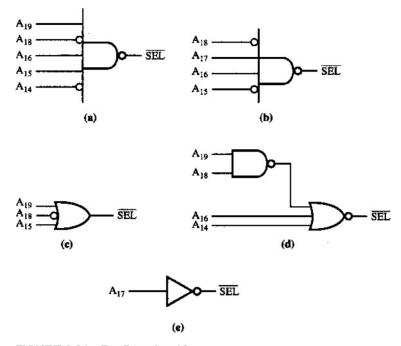

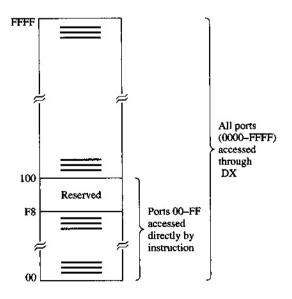

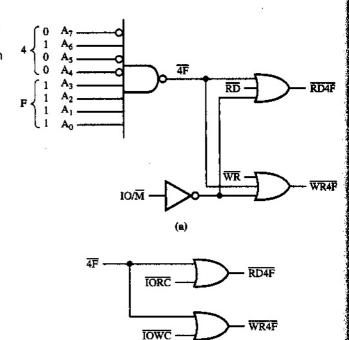

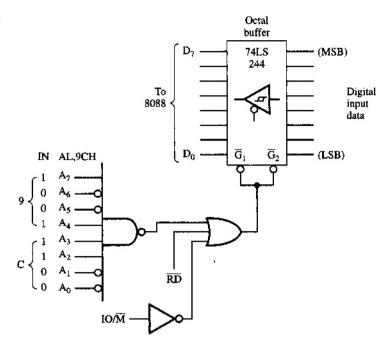

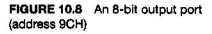

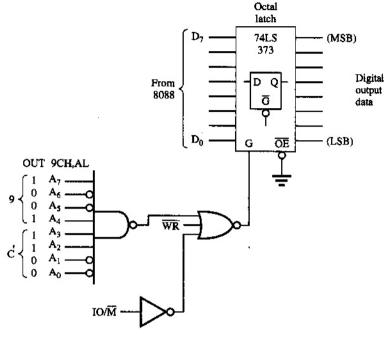

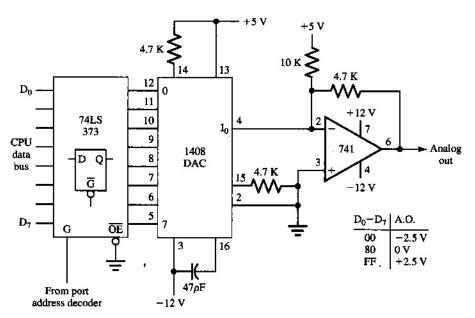

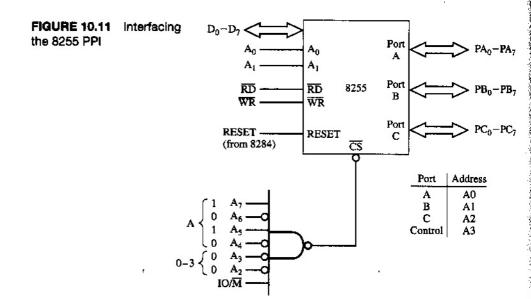

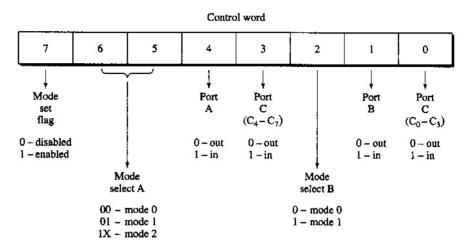

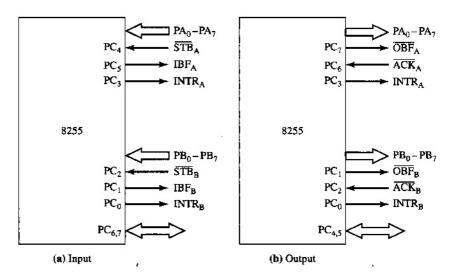

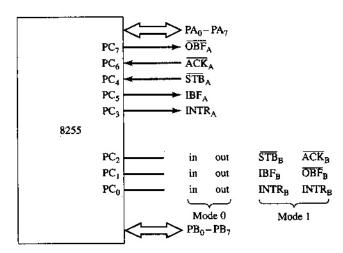

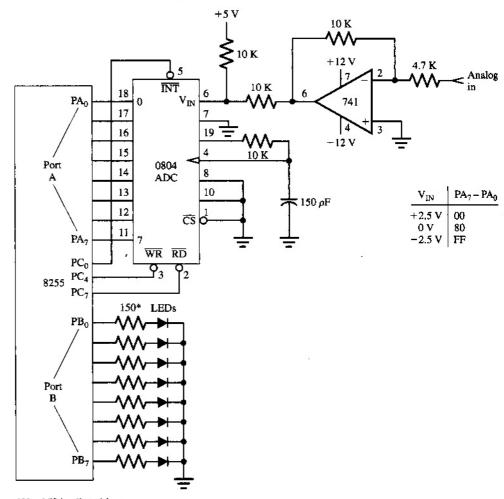

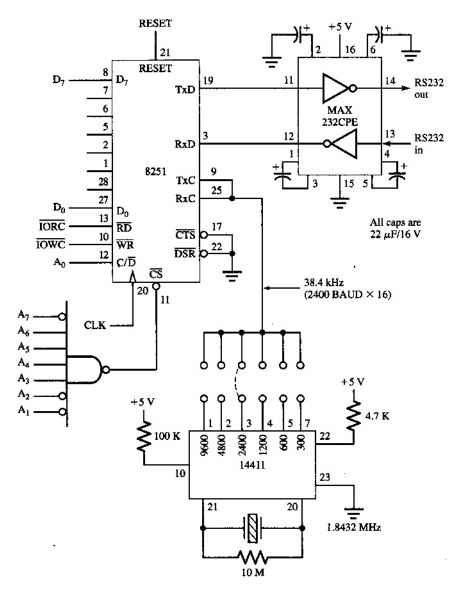

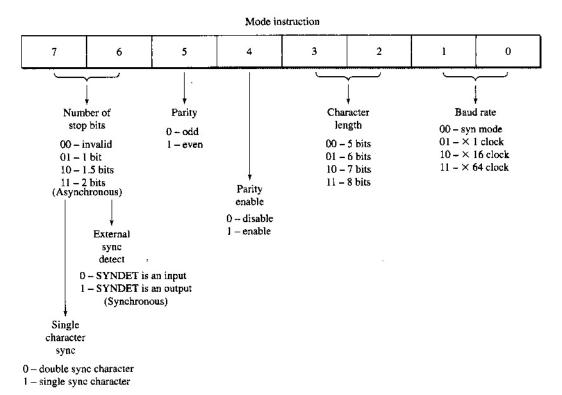

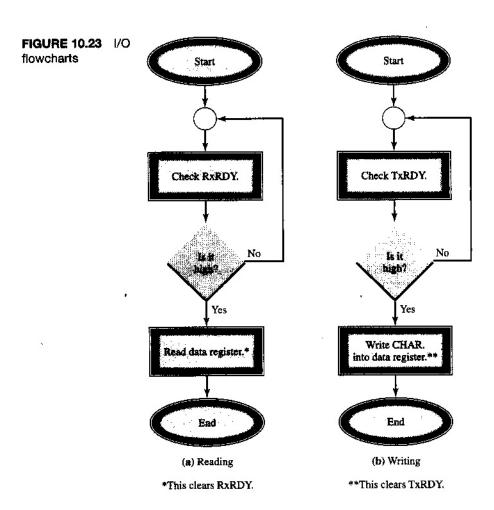

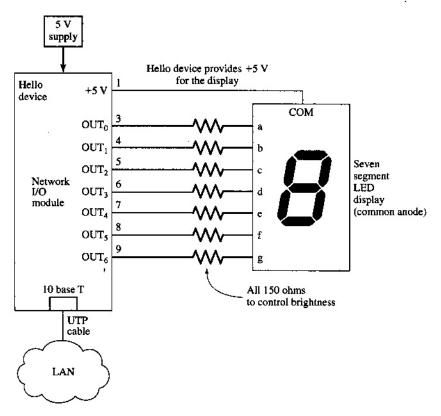

The I/O system is covered in **Chapter 10**, I/O System Design. In this chapter the difference between the processor's memory space and port space is covered, as are the techniques needed to design port address decoders. Two 8085-based peripherals are covered: the 8255<sup>TM</sup> parallel interface adapter and the 8251 UART<sup>TM</sup>, with 8088 interfacing and programming examples provided.

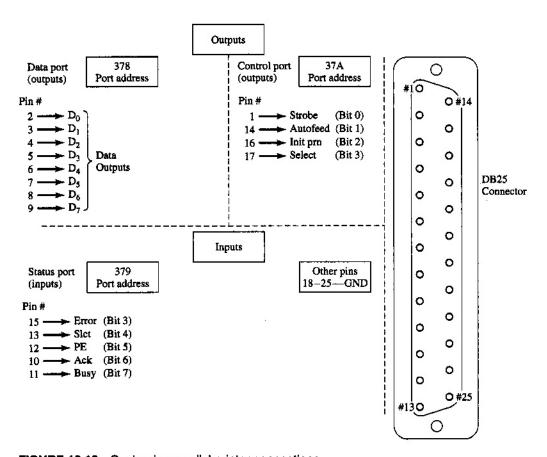

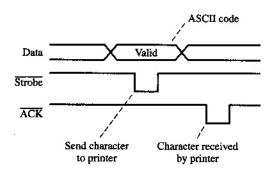

Interfacing with the 80x86 is the subject of Chapter 11. In this chapter, three peripherals designed to interface with the 80x86 are examined. These peripherals implement interval timing, interrupt control, and floating-point operations. Programming and interfacing are discussed, with specific examples. Several examples are included that show how interfacing is performed with the Personal Computer.

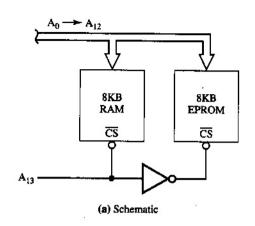

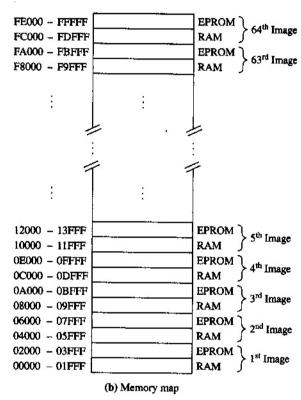

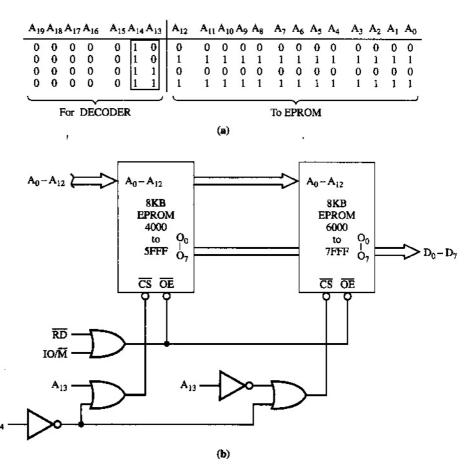

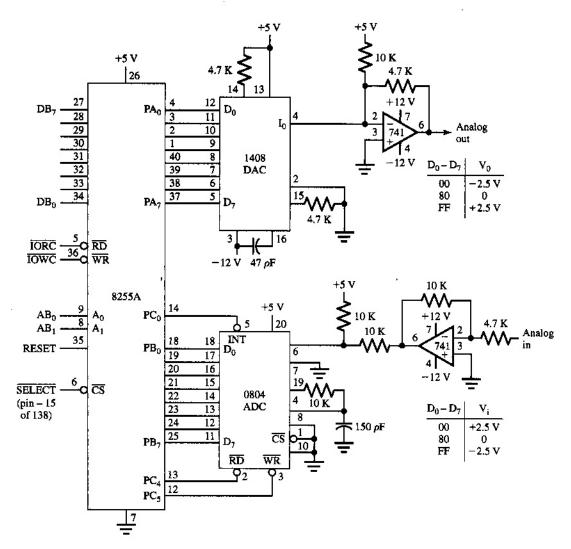

Many textbooks rarely cover hardware and software with an equal amount of detail. This book was written to give equal treatment to both, culminating in a practical exercise: building and programming your own single-board computer! Chapter 12, Building a Working 8088 System, is included to give students a chance to design, build, and program their own 8088-based computers. The system contains 8KB of EPROM, 8KB of RAM, a serial I/O device, a parallel I/O device, and 8-bit D/A and A/D converters. Future memory expansion is built in. The hardware is designed first, followed by design of the software monitor program.

Some books choose to explain the operation of a commercial system, such as the SDK-86<sup>TM</sup>. This approach is certainly worthwhile, but does not give the student the added advantage of knowing *why* certain designs were used. The hardware and software designs in Chapter12 are sprinkled with many questions, which are used to guide the design toward its final goal.

The single-board computer presented in Chapter 12 can be easily wire-wrapped in a short period of time (some students have constructed a working computer in seven days), directly from the schematics provided in the chapter. It is reasonable to say that most students can build a working system in one semester.

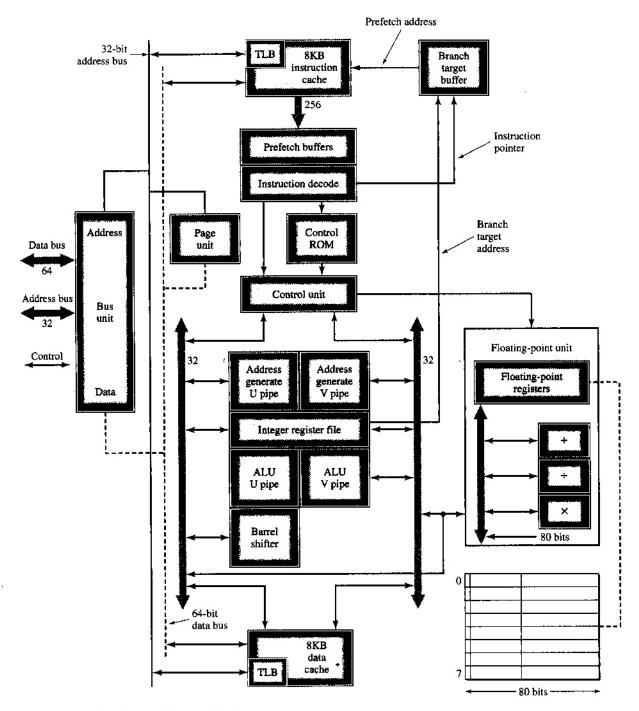

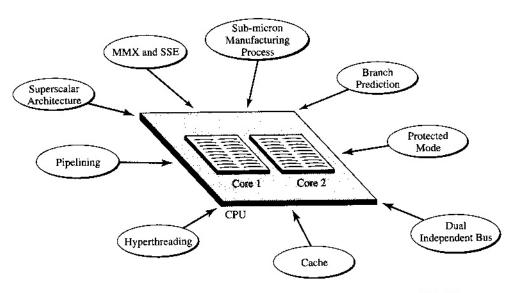

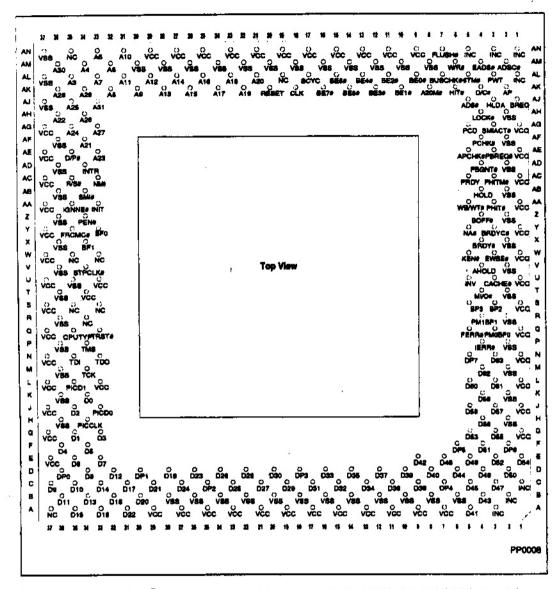

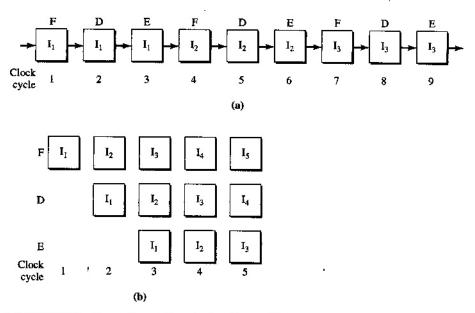

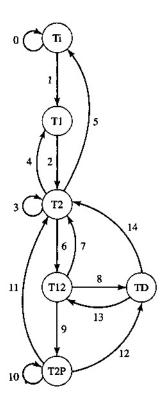

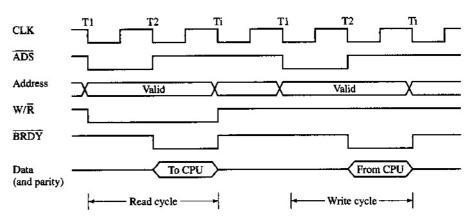

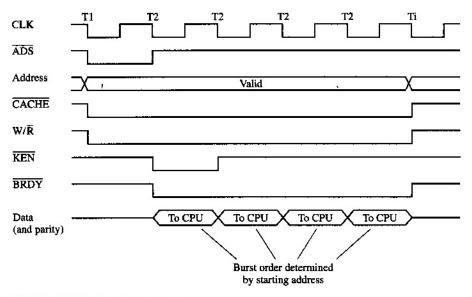

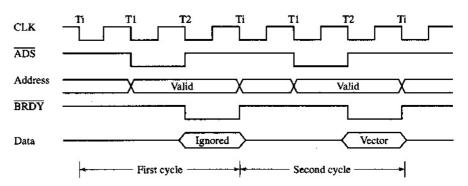

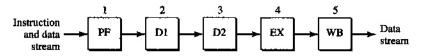

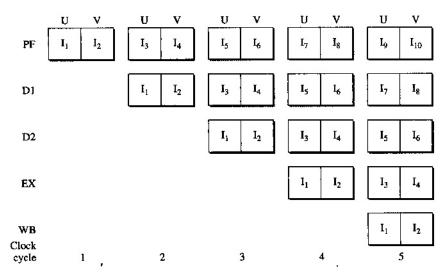

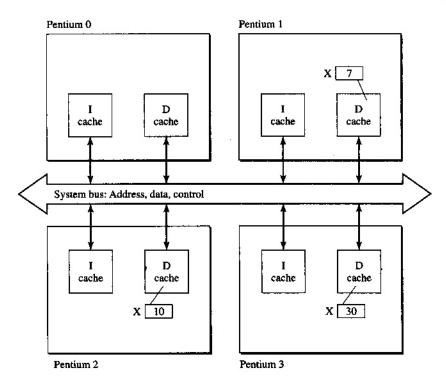

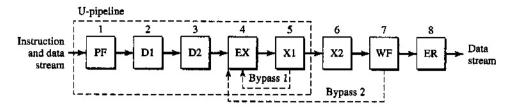

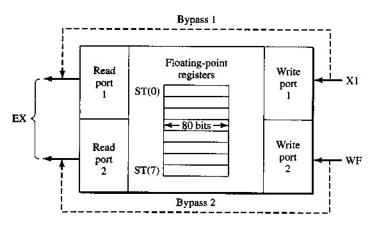

The hardware operation of the first Pentium CPU is covered in Chapter 13, Hardware Details of the Pentium. Descriptions of each CPU pin are included, as are explanations of the various methods employed by the Pentium to access data over its buses. The operation of the Pentium's superscaler architecture, internal pipelining, branch prediction, instruction and data caches, and floating-point unit are discussed.

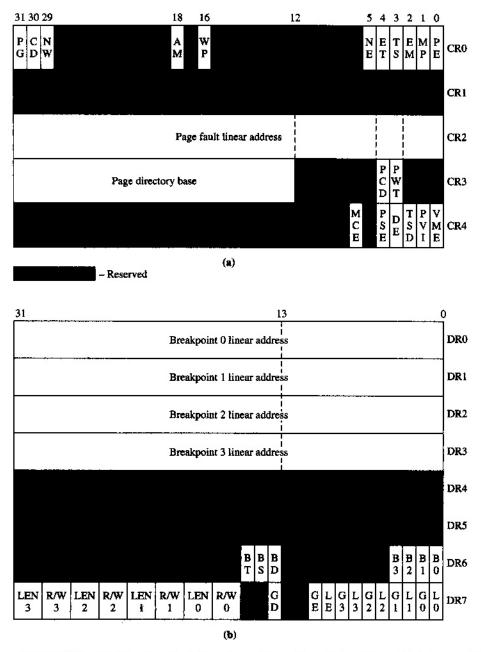

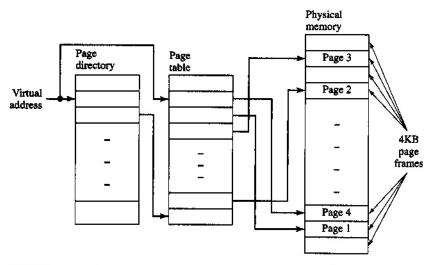

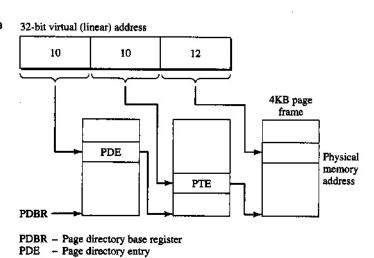

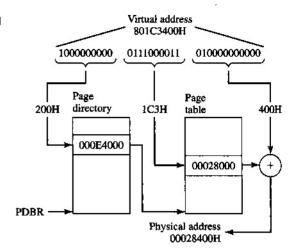

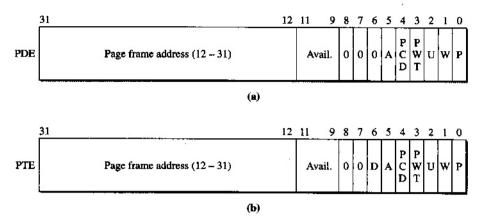

Chapter 14, Protected-Mode Operation, presents the details associated with protected-mode operation. The virtual memory techniques made possible by the use of segments and paging are explained. Important issues such as protection, exceptions, multitasking, and input/output are also discussed. Virtual-8086 mode is also covered.

Finally, Chapter 15, The Pentium II and Beyond, takes a guided tour of the architectural changes and improvements in the Pentium line, beginning with the Pentium II, and ending with a look into Intel's future plans for their microprocessor technology. Mobile processors are also examined, with emphasis placed on their special need for low power.

#### USES OF THE BOOK

Due to the information presented, some chapters are much longer than others. Even so, it is possible to cover certain sections of selected chapters out of sequence, or to pick and choose sections from various chapters. Chapters 3 and 4 could be covered in this way, with emphasis placed on additional addressing modes or groups of instructions at a rate deemed appropriate by the instructor. Some instructors may wish to cover hardware (Chapters 8 through 12), before programming (Chapters 3 through 7). There is no reason this cannot be done.

To aid the instructor, answers to selected odd-numbered end-of-chapter study questions are included in the text and are also provided in a detailed solutions manual. The solutions manual is designed in such a way that solutions to all odd-numbered questions are grouped together, followed by solutions to all even-numbered questions. This allows the instructor to release selected odd-only or even-only answers to students, while retaining others for testing purposes.

In summary, over 250 illustrations and 70 different applications are used to give the student sufficient exposure to the 80x86. The added benefit of Chapter 12, where a working system is developed, makes this book an ideal choice for a student wishing to learn about microprocessors. The material in Chapters 13 through 15 lays the groundwork for more advanced hardware and software development. Furthermore, even though this book deals only with the 80x86 family, the serious microprocessor student should also be exposed to other CPUs as well. But to try to cover two or more different microprocessors in one text does not do either microprocessor justice. For this reason, all attention is paid to the 80x86 family and not to other CPUs.

#### THE COMPANION CD

The CD included with the book contains all of the source files presented in the book. The files are stored in separate directories related to their specific chapters. In addition, the object code library NUMOUT.LIB from Chapter 7 and the various binary and executable files related to the single-board computer from Chapter 12 are also included. Many useful data sheets and references are provided in PDF format, and there are also fifteen software laboratory experiments to challenge the student.

#### **ACKNOWLEDGMENTS**

I would like to thank my editor, Michelle Ruelos Cannistraci for her help while I was putting this book together. In addition, I would like to thank my copyeditor, Libby Larson, as well as Benjamin Gleeksman who managed the book through production. I especially wish to thank Steve Helba, who offered the opportunity to give this book a new life.

The following individuals provided many useful comments and I am grateful for their advice:

Lance Crimm, Southern Polytechnic State University, Marietta, GA Sang Lee, DeVry University, Addison, IL Faramarz Mortezaie, DeVry University, Fremont, CA Max Rabiee, University of Cincinnati, Cincinnati, OH Lew Rakocy, DeVry University, Columbus, OH

James L. Antonakos antonakos\_j@sunybroome.edu http://www.sunybroome.edu/~antonakos\_j

# **BRIEF CONTENTS**

| PART I:   | INTRODUCTION  1. MICROPROCESCOR RACER SYSTEMS                         |                  |

|-----------|-----------------------------------------------------------------------|------------------|

|           | 1. MICROPROCESSOR-BASED SYSTEMS                                       | 3                |

|           | 2. AN INTRODUCTION TO THE 80x86 MICROPROCESSOR FAMILY                 | 21               |

| PART II:  | SOFTWARE ARCHITECTURE                                                 |                  |

|           | 3. 80x86 INSTRUCTIONS PART 1: ADDRESSING MODES, FLAGS, DATA TRANSFER. |                  |

|           | AND STRING INSTRUCTIONS                                               | 53               |

|           | 4. 80x86 INSTRUCTIONS PART 2: ARITHMETIC, LOGICAL, BIT MANIPULATION,  |                  |

|           | PROGRAM TRANSFER, AND PROCESSOR CONTROL INSTRUCTIONS                  | 99               |

|           | 5. INTERRUPT PROCESSING                                               | 141              |

| PART III: | PROGRAMMING                                                           |                  |

|           | 6. AN INTRODUCTION TO PROGRAMMING THE 80x86                           | 165              |

|           | 7. ADVANCED PROGRAMMING APPLICATIONS                                  | 222              |

| PART IV:  | HARDWARE ARCHITECTURE                                                 |                  |

|           | 8. HARDWARE DETAILS OF THE 8088                                       | 287              |

|           | 9. MEMORY SYSTEM DESIGN                                               | 308              |

|           | 10. I/O SYSTEM DESIGN                                                 | 337              |

|           | 11. INTERFACING WITH THE 80x86                                        | 366              |

|           | 12. BUILDING A WORKING 8088 SYSTEM                                    | 415              |

| PART V:   | ADVANCED TOPICS                                                       |                  |

|           | 13. HARDWARE DETAILS OF THE PENTIUM                                   | 457              |

|           | 14. PROTECTED-MODE OPERATION                                          | 489              |

|           | 15. THE PENTIUM II AND BEYOND                                         | 522              |

|           | APPENDIXES                                                            | 540              |

|           | SOLUTIONS AND ANSWERS TO SELECTED ODD-NUMBERED STUDY QUESTIONS        | 5 <del>4</del> 0 |

|           | INDEX                                                                 | 605              |

|           |                                                                       | 000              |

# **CONTENTS**

PART I:

| INTRODU                                                                              | UCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                                        | ROPROCESSOR-BASED SYSTEMS Introduction 3 Evolution of Microprocessors 4 System Block Diagram 5 Microprocessor Operation 8 Hardware/Software Requirements 10 The Personal Computer 11 Developing Software for the Personal Computer 14 Troubleshooting Techniques 18 Summary 18 Study Questions 19                                                                                                                                                                  | 3  |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.10<br>2.11<br>2.12<br>2.13 | INTRODUCTION TO THE 80x86 MICROPROCESSOR FAMILY  Introduction 22 Real-Mode and Protected-Mode Operation 22 The Software Model of the 80x86 Family 23 Processor Registers 24 Data Organization 27 Instruction Types 30 Addressing Modes 35 Interrupts 40 The 8086: The First 80x86 Machine 41 A Summary of the 80286 43 A Summary of the 80386 44 A Summary of the 80486 45 A Summary of the Pentium 46 Troubleshooting Techniques 48 Summary 48 Study Questions 49 | 21 |

| PART II:  | SOFTWARE ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|           | 3. 80x86 INSTRUCTIONS, PART 1: ADDRESSING MODES, FLAGS, DATA TRANSFER, AND STRING INSTRUCTIONS 3.1 Introduction 53 3.2 Assembly Language Programming 54 3.3 Instruction Types 59 3.4 Addressing Modes 60 3.5 The Processor Flags (Condition Codes) 70 3.6 Data Transfer Instructions 74 3.7 String Instructions 89 3.8 Troubleshooting Techniques 96 Summary 96 Study Questions 96                                                                                                       | 5   |

|           | 4. 80x86 INSTRUCTIONS, PART 2: ARITHMETIC, LOGICAL, BIT MANIPULATION, PROGRAM TRANSFER, AND PROCESSOR CONTROL INSTRUCTIONS 4.1 Introduction 99 4.2 Arithmetic Instructions 100 4.3 Logical Instructions 110 4.4 Bit Manipulation Instructions 116 4.5 Program Transfer Instructions 121 4.6 Processor Control Instructions 134 4.7 How an Assembler Generates Machine Code 135 4.8 The Beauty of Relocatable Code 136 4.9 Troubleshooting Techniques 137 Summary 137 Study Questions 138 | 99  |

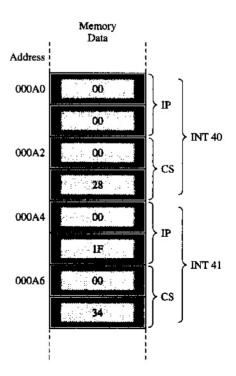

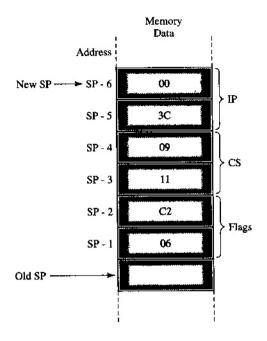

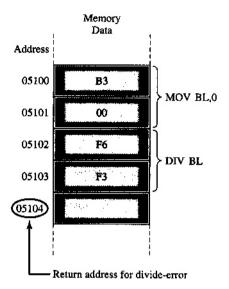

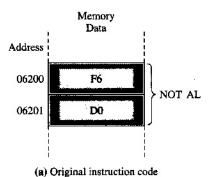

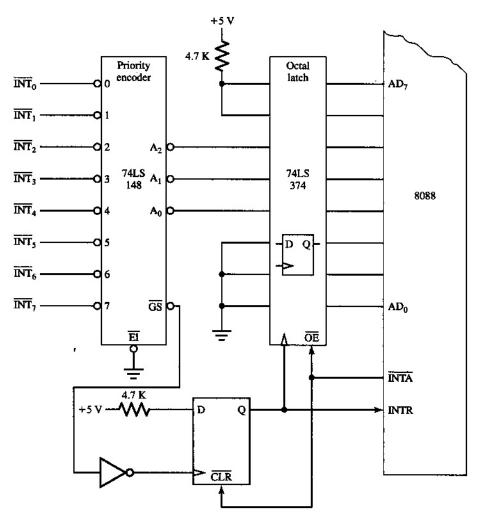

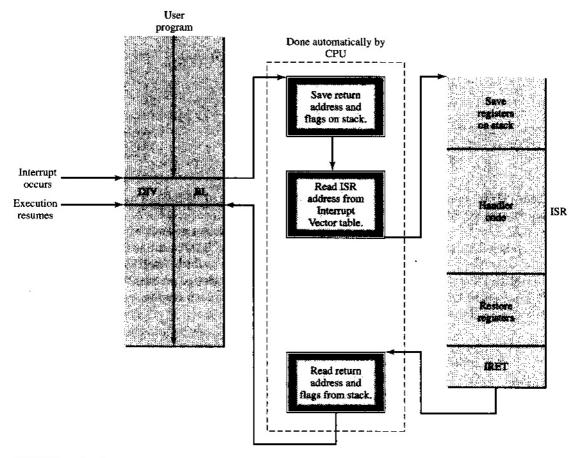

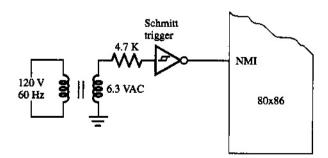

|           | 5. INTERRUPT PROCESSING 5.1 Introduction 141 5.2 Hardware and Software Interrupts 142 5.3 The Interrupt Vector Table 143 5.4 The Interrupt Processing Sequence 146 5.5 Multiple Interrupts 147 5.6 Special Interrupts 148 5.7 Interrupt Service Routines 154 5.8 Troubleshooting Techniques 159 Summary 159 Study Questions 159                                                                                                                                                          | 141 |

| PART III: | PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

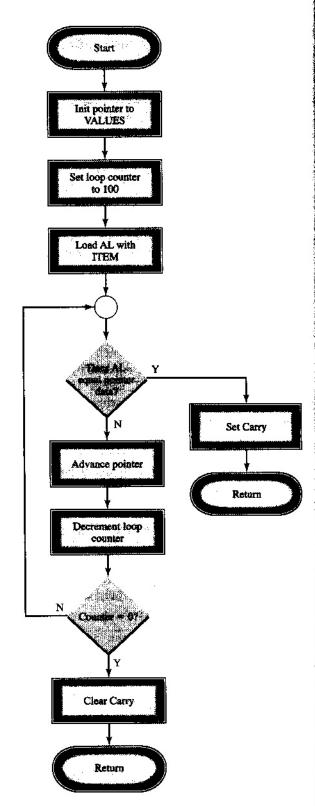

|           | 6. AN INTRODUCTION TO PROGRAMMING THE 80x86 6.1 Introduction 166 6.2 Tackling a Large Programming Assignment 166 6.3 Writing a Software Tester 172 6.4 Data Gathering 174 6.5 Searching Data Tables 177 6.6 String Operations 180 6.7 Sorting 185                                                                                                                                                                                                                                        | 165 |

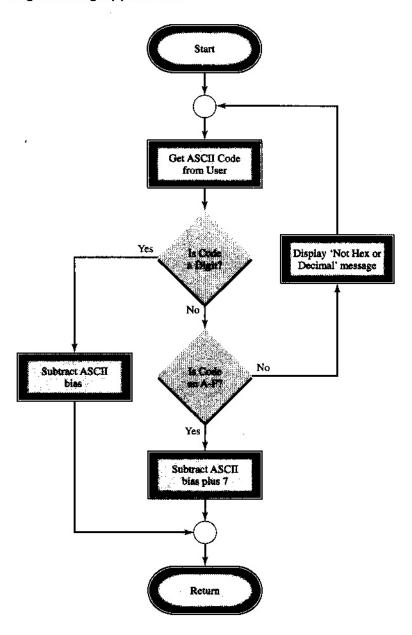

|     | 6.9<br>6.10<br>6.11 | Computational Routines 187 Control Applications 201 Number Conversions 208 Data Structures 211 Troubleshooting Techniques 217 Summary 218 Study Question 219 Additional Programming Exercises 219 | ,   |

|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.  |                     | ANCED PROGRAMMING APPLICATIONS                                                                                                                                                                    | 222 |

|     |                     | Introduction 222                                                                                                                                                                                  |     |

|     |                     | Using the EXTRN and PUBLIC Assembler Directives 223                                                                                                                                               |     |

|     |                     | Using Macros 226                                                                                                                                                                                  |     |

|     |                     | Instruction Execution Times 234 Working with Interpret Vectors 237                                                                                                                                |     |

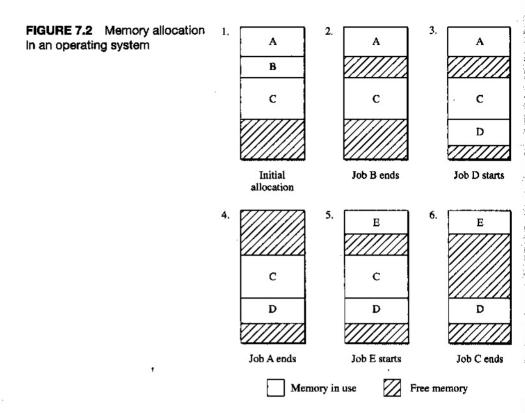

|     |                     | Working with Interrupt Vectors 237 Multitasking 240                                                                                                                                               |     |

|     |                     | Memory Management 245                                                                                                                                                                             |     |

|     |                     | Using the Mouse 251                                                                                                                                                                               |     |

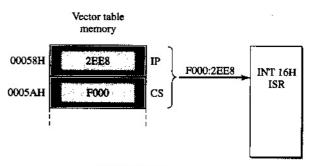

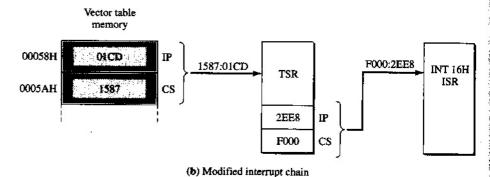

|     |                     | Writing a Memory-Resident Program 254                                                                                                                                                             |     |

|     |                     | TICTAC: A Game for a Change 260                                                                                                                                                                   |     |

|     |                     | Protected-Mode Detection 264                                                                                                                                                                      |     |

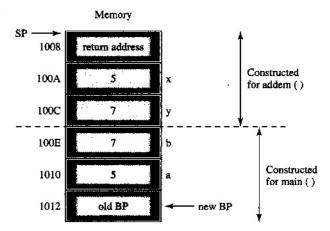

|     | 7.12                | Interfacing C with Assembly Language 266                                                                                                                                                          |     |

|     |                     | Assembly Language in the Windows Environment 274                                                                                                                                                  |     |

|     |                     | Assembly Language in the Linux Environment 277                                                                                                                                                    |     |

|     | 7.15                | Troubleshooting Techniques 281                                                                                                                                                                    |     |

|     |                     | Summary 281                                                                                                                                                                                       |     |

|     |                     | Study Questions 282                                                                                                                                                                               |     |

|     |                     | Additional Programming Exercises 282                                                                                                                                                              |     |

| HAR | DWA                 | ARE ARCHITECTURE                                                                                                                                                                                  |     |

| 8.  | HΔR                 | DWARE DETAILS OF THE 8088                                                                                                                                                                         | 287 |

| ٠.  |                     | Introduction 287                                                                                                                                                                                  | 201 |

|     |                     | CPU Specifications 288                                                                                                                                                                            |     |

|     |                     | CPU Pin Descriptions 290                                                                                                                                                                          |     |

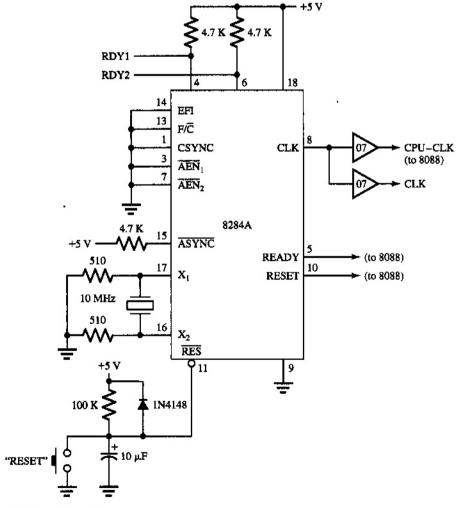

|     |                     | The 8284 Clock Generator 296                                                                                                                                                                      |     |

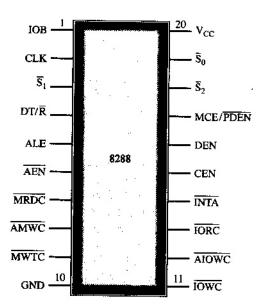

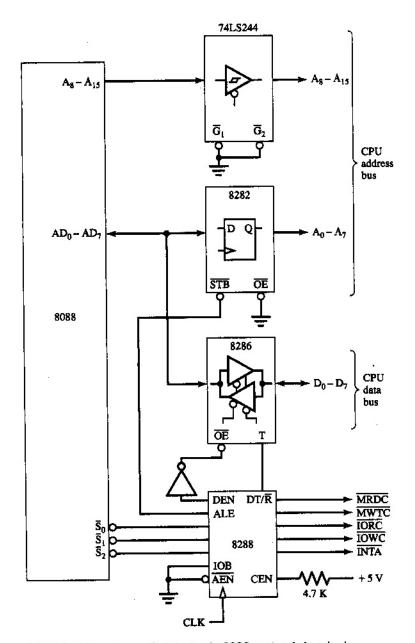

|     | 8.5                 | The 8288 Bus Controller 298                                                                                                                                                                       |     |

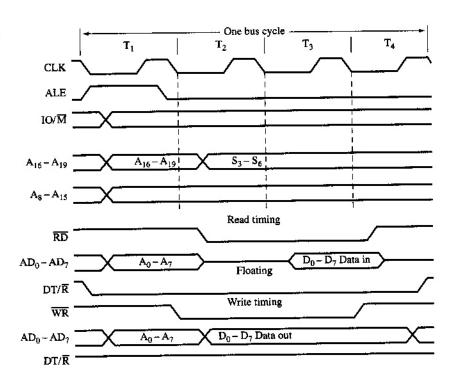

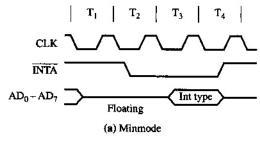

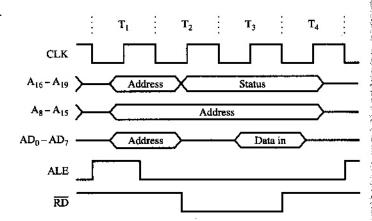

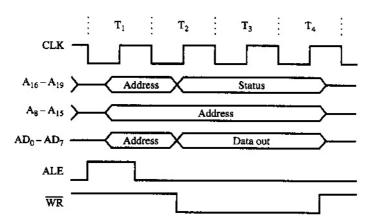

|     | 8.6                 | System Timing Diagrams 300                                                                                                                                                                        |     |

|     |                     | Early Personal Computer Bus Standards 303                                                                                                                                                         |     |

|     | 8.8                 | Troubleshooting Techniques 305.                                                                                                                                                                   |     |

|     |                     | Summary 305                                                                                                                                                                                       |     |

|     |                     | Study Questions 306                                                                                                                                                                               |     |

| 9.  | MEN                 | MORY SYSTEM DESIGN                                                                                                                                                                                | 308 |

|     | 9.1                 | Introduction 308                                                                                                                                                                                  |     |

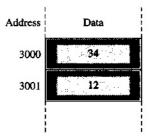

|     |                     | The 8088 Address and Data Buses 309                                                                                                                                                               |     |

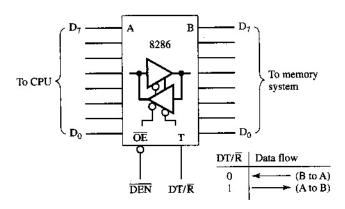

|     |                     | Bus Buffering 309                                                                                                                                                                                 |     |

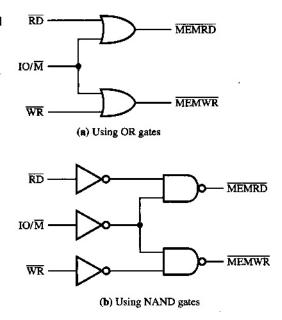

|     |                     | Accessing Memory 311                                                                                                                                                                              |     |

|     |                     | Designing a Memory Address Decoder 313                                                                                                                                                            |     |

|     |                     | Partial-Address Decoding 319                                                                                                                                                                      |     |

|     | 9.7                 | Generating Wait States 322                                                                                                                                                                        |     |

**PART IV:**

|         |     | <ul> <li>9.8 A Complete RAM/EPROM Memory 323</li> <li>9.9 Dynamic RAM Interfacing 325</li> <li>9.10 Direct Memory Access 331</li> <li>9.11 Memory-Mapped I/O 332</li> <li>9.12 Troubleshooting Techniques 333</li> <li>Summary 334</li> <li>Study Questions 334</li> </ul>                                                                                                                                                   |     |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|         | 10. | i/O SYSTEM DESIGN  10.1 Introduction 337  10.2 The 8088 Port Addressing Space 338  10.3 Designing a Port Address Decoder 339  10.4 Operation of a Buffered Input Port 342  10.5 Operation of a Latched Output Port 343  10.6 Simple I/O Applications 344  10.7 Parallel Data Transfer: The 8255 PPI 347  10.8 Serial Data Transfer: The 8251 UART 354  10.9 Troubleshooting Techniques 362  Summary 362  Study Questions 362 | 337 |

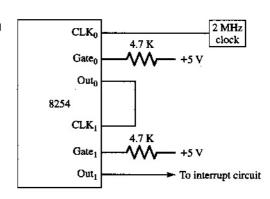

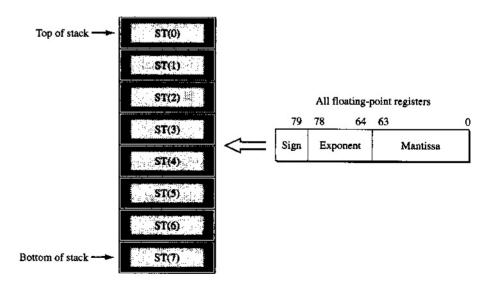

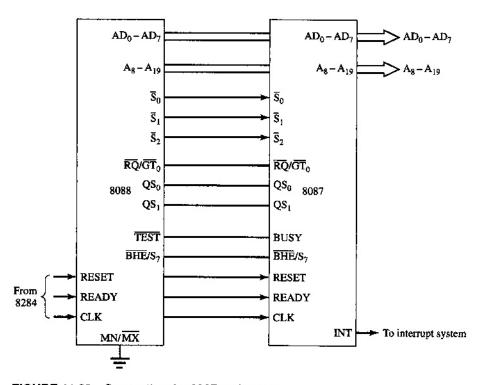

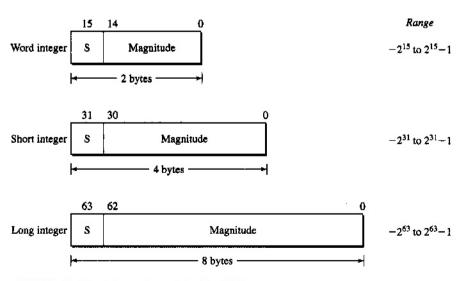

|         | 11. | INTERFACING WITH THE 80x86  11.1 Introduction 366  11.2 The 8259 Programmable Interrupt Controller 367  11.3 The 8254 Programmable Interval Timer 376  11.4 The Floating-Point Unit (80x87 Coprocessor) 386  11.5 Interfacing with the Personal Computer 399  11.6 Troubleshooting Techniques 411  Summary 412  Study Questions 412                                                                                          | 366 |

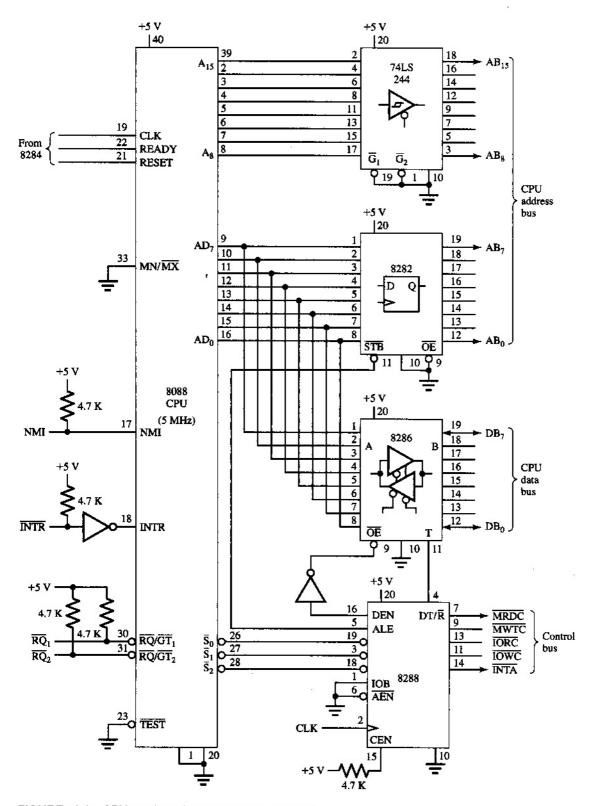

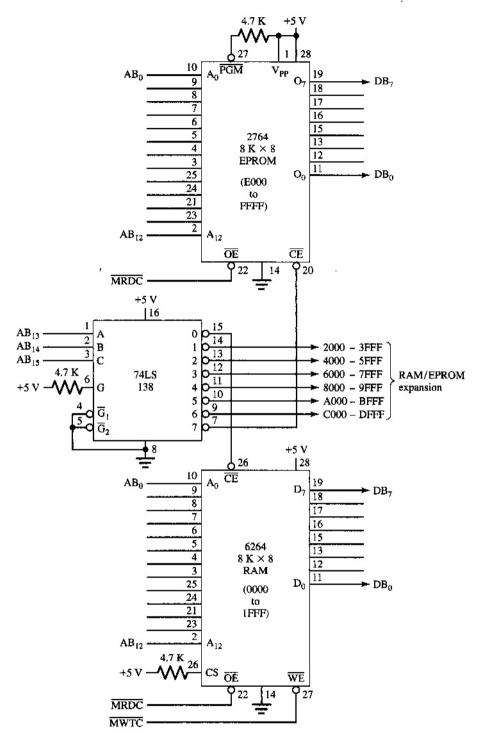

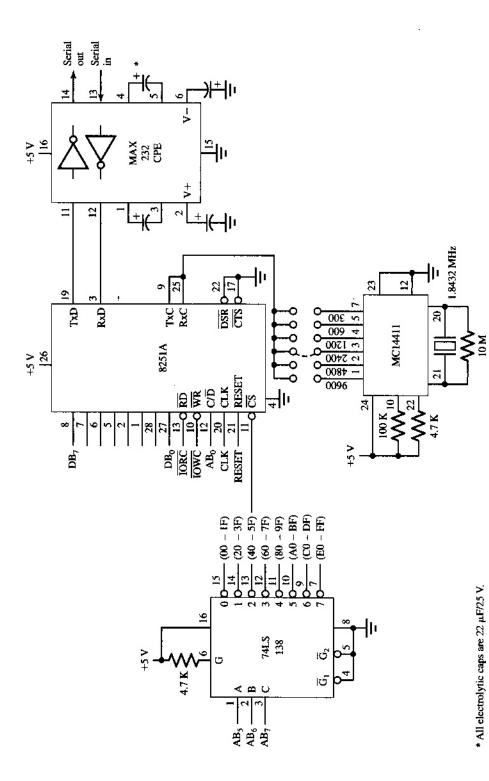

|         | 12. | BUILDING A WORKING 8088 SYSTEM  12.1 Introduction 415  12.2 Minimal System Requirements 416  12.3 Designing the Hardware 416  12.4 The Minimal System Parts List 426  12.5 Construction Tips 426  12.6 Writing the Software Monitor 427  12.7 A Sample Session with the Single-Board Computer 448  12.8 Troubleshooting Techniques 450  Summary 451  Study Questions 451                                                     | 415 |

| PART V: | ΑD\ | ANCED TOPICS                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

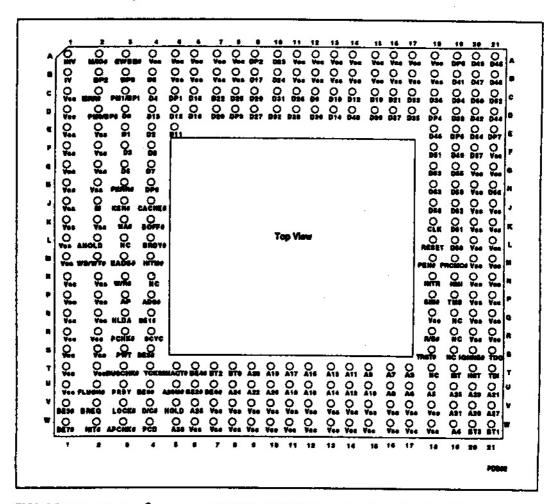

|         | 13. | HARDWARE DETAILS OF THE PENTIUM  13.1 Introduction 457  13.2 CPU Pin Descriptions 458  13.3 RISC Concepts 465  13.4 Bus Operations 468  13.5 The Pentium's Superscalar Architecture 473                                                                                                                                                                                                                                      | 457 |

CONTENTS xvii

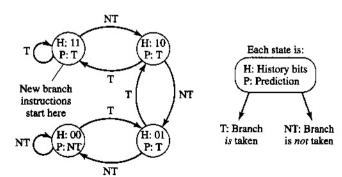

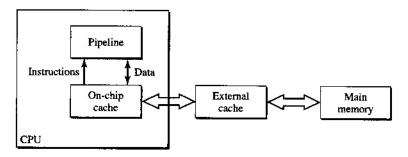

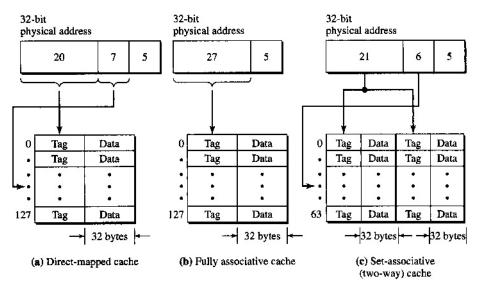

|     | <ul> <li>13.6 Pipelining 474</li> <li>13.7 Branch Prediction 475</li> <li>13.8 The Instruction and Data Caches 477</li> <li>13.9 The Floating-Point Unit 483</li> <li>13.10 Troubleshooting Techniques 485</li> <li>Summary 486</li> <li>Study Questions 486</li> </ul>                                                                                      |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

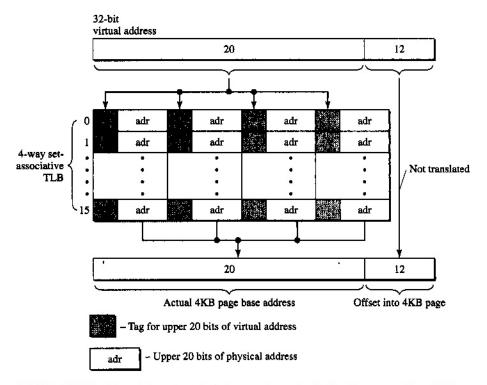

| 14. | 14.1 Introduction 489 14.2 Segmentation 492 14.3 Paging 496 14.4 Protection 500 14.5 Multitasking 502 14.6 Exceptions and Interrupts 506 14.7 Input/Output 513 14.8 Virtual-8086 Mode 514 14.9 A Protected-Mode Application 516 14.10 Troubleshooting Techniques 519 Summary 520                                                                             | 489 |

| 15. | THE PENTIUM II AND BEYOND  15.1 Introduction 522  15.2 The Pentium Pro 523  15.3 The Pentium II 526  15.4 The Pentium III 528  15.5 The Pentium 4 529  15.6 The Celeron 532  15.7 The Xeon 532  15.8 IA-64 Architecture: The Itanium and Itanium 2 533  15.9 Intel's Mobile CPUs 535  15.10 Troubleshooting Techniques 537  Summary 538  Study Questions 538 | 522 |

|     | APPENDIXES  A. Instruction Execution Times 540  B. A Review of Number Systems, Binary Arithmetic, and Logic Functions 548  C. Assembler Reference 556  D. DEBUG and CodeView Reference 560  E. ASCII Character Set 576  F. MMX Technology 578                                                                                                                | 540 |

|     | SOLUTIONS AND ANSWERS TO SELECTED ODD-NUMBERED STUDY QUESTIONS                                                                                                                                                                                                                                                                                               | 591 |

|     | INDEX                                                                                                                                                                                                                                                                                                                                                        | 605 |

# PART 1

### Introduction

- 1 Microprocessor-Based Systems

- 2 An Introduction to the 80x86 Microprocessor Family

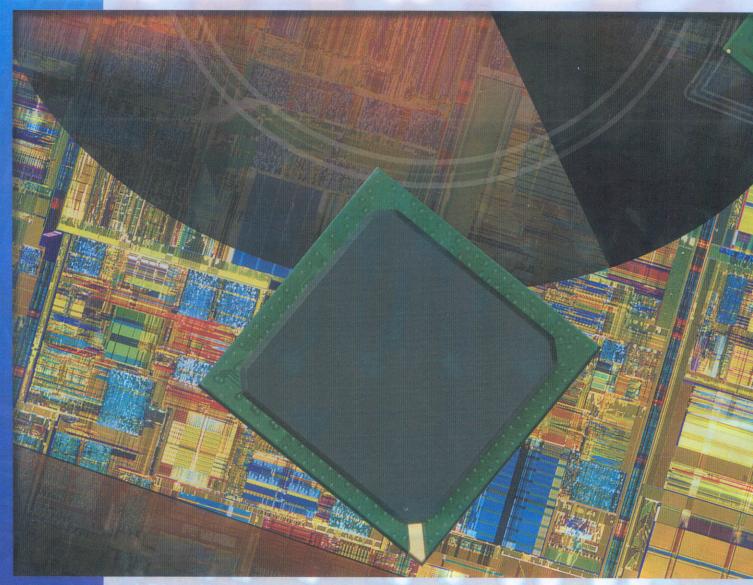

A typical Pentium motherboard for the Personal Computer

### **CHAPTER 1**

### Microprocessor-Based Systems

#### **OBJECTIVES**

In this chapter you will learn about:

- The block diagram of a microprocessor-based system and the function of each section

- The processing cycle of a microprocessor

- · The way software is used to initialize hardware and peripherals

- The history of the microprocessor and of the different generations of computers

- The technique used to create software for the personal computer

- Some typical errors encountered during program development

#### **KEY TERMS**

Assembler Interrupt Random access memory Read-only memory Machine language Assembly language Math coprocessor Source file Cache Central processing unit Microcontrollers System bus Motherboard Watchdog monitor Direct memory access **Expansion slots** Nonvolatile memory

#### 1.1 INTRODUCTION

What is a microprocessor? You may have heard the term, or even looked inside your personal computer to locate it. A microprocessor is a digital machine capable of executing many different software instructions and controlling a wide variety of electronic devices. The invention of the microprocessor has had a profound impact on many aspects of our lives. Today even the most mundane chores are being accomplished under its supervision—which allows us more time for other productive endeavors. Even a short list of the devices using the microprocessor shows how dependent on it we have become:

- 1. Pocket calculators

- 2. Digital watches (some with calculators built in)

- 3. Automatic tellers (at banks and food stores)

- 4. Cell phones

- 5. CD and MP3 players

- 6. Home security and control devices

- 7. Realistic video games

- 8. Talking dolls and other toys

- 9. VCRs and DVD players

- 10. Personal computers

- 11. PDAs

- 12. Digital cameras

The purpose of this chapter is to show how a microprocessor is used in a small system and to introduce the operation of the personal computer. We will see what types of hardware may be connected to the microprocessor, and why each type is needed. We will also see how software is used to control the hardware, and how that software can be developed.

Section 1.2 shows how the microprocessor has evolved over time, from the initial 4-bit machines to today's 32-bit processors. Section 1.3 covers the block diagram of a typical microprocessor-based system and explains each functional unit. Section 1.4 explains the basic operation of a microprocessor. Section 1.5 discusses the hardware and software requirements of a small microprocessor control system. Section 1.6 brings the material of the first five sections together in a technical description of the personal computer. Section 1.7 shows how software is developed for, and used by, the personal computer. Finally, section 1.8 introduces the first of a series of troubleshooting techniques.

#### 1.2 EVOLUTION OF MICROPROCESSORS

We have come a long way since the early days of computers, when ENIAC (Electronic Numerical Integrator and Computer) was state of the art and occupied thousands of feet of floor space. Constructed largely of vacuum tubes, it was slow, prone to breakdowns, and performed a limited number of instructions. Even so, ENIAC ushered in what was known as the first generation of electronic computers.

Today, thanks to advances in technology, we have complete computers that fit on a piece of silicon no larger than your fingernail and that far outperform ENIAC.

With the invention of the transistor, computers shrank in size and increased in power, leading to the second generation of computers. Third-generation computers came about with the invention of the integrated circuit, which allowed hundreds of transistors to be packed on a small piece of silicon. The transistors were connected to form logic elements, the basic building blocks of digital computers. With third-generation computers, we again saw a decrease in size and increase in computing power. Machines like the 4004<sup>TM</sup> and 8008<sup>TM</sup> by Intel<sup>®</sup> found some application in simple calculators, but they were limited in computation power and memory addressing capability. When improvements in integrated circuit technology enabled us to place *thousands* of transistors on the same piece of silicon, computers really began to increase in power. This new technology, called large-scale integration (LSI), was even faster than the previous medium- and small-scale integration (MSI and SSI, respectively) technologies, which dealt with only tens or hundreds of transistors on a chip. LSI technology created the fourth generation of computers. An advanced form

of LSI technology, VLSI, meaning very large scale integration, is now being used to increase processing power.

The first microprocessors that became available with third-generation computers had limited instruction sets, slow execution speed, and limited memory addressing, and thus restricted computing abilities. Although they were suitable for use in electronic calculators, they simply did not have the power needed to operate more complex systems, such as guidance systems or scientific applications. Even some of the early fourth-generation microprocessors had limited capabilities because of the lack of addressing modes and instruction types. Eight-bit machines like the 8080<sup>TM</sup>, Z80<sup>TM</sup>, and 6800<sup>TM</sup> were indeed more advanced than previous microprocessors, but they still did not possess multiply and divide instructions. How frustrating and time consuming to have to write a program to do these operations!

Within the last few decades, microprocessor technology has improved tremendously. Thirty-two-bit processors can now multiply and divide, operate on many different data types (4-, 8-, 16-, 32-bit numbers), and address billions of bytes of information. Processors of the 1970s were limited to 64KB of memory for programs and data, a small amount of memory by today's standards.

Each new microprocessor to hit the market boasts a fancier instruction set and faster clock speed, and our need for faster and better processors keeps growing. Taking a different approach, a technology called RISC (Reduced Instruction Set Computer) has gained acceptance. This 'technology is based on the fact that most microprocessors use only a small portion of their entire instruction set. By designing a machine that uses only the more common types of instructions, processing speed can be increased without the need for a significant advance in integrated circuit technology. The Pentium microprocessor, manufactured by Intel, uses many of the architectural techniques employed by RISC machines.

Why the need for super-fast machines? Consider a microprocessor dedicated to displaying three-dimensional color images on a video screen. Rotating the three-dimensional image around an imaginary axis in real time (in only a few seconds or less) may require millions or even billions of calculations. A slow microprocessor could not do the job.

Eventually we will see fifth-generation computers. The whole artificial intelligence movement is pushing toward that goal, with the desired outcome being the production of a machine that can think. Until then, we will have to make the best use of the technology we have available.

#### 1.3 SYSTEM BLOCK DIAGRAM

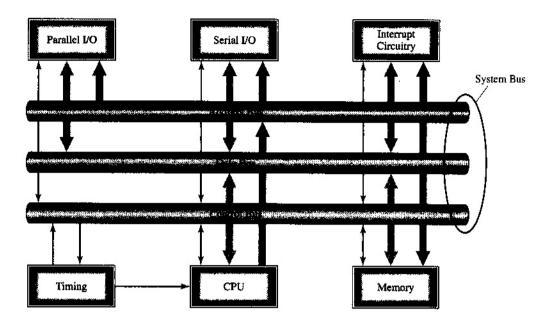

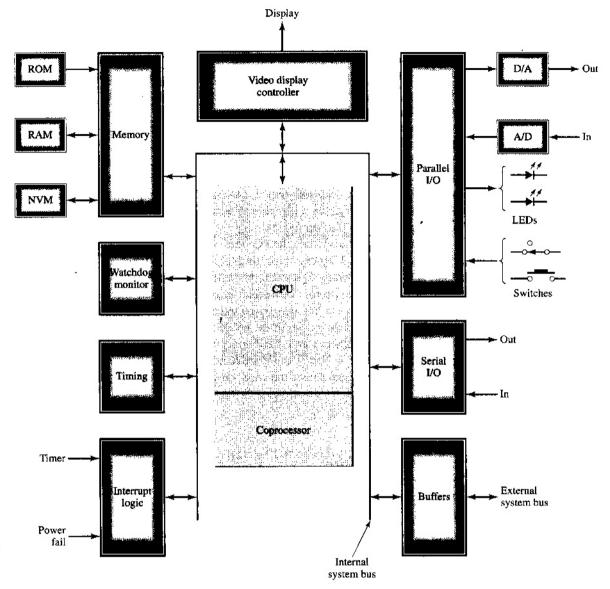

Any microprocessor-based system must, of necessity, have some standard elements such as memory, timing, and input/output (I/O). Depending on the application, other exotic circuitry may be necessary as well. Analog-to-digital (A/D) converters and their counterparts, digital-to-analog (D/A) converters, interval timers, math coprocessors, complex interrupt circuitry, speech synthesizers, and video display controllers are just a few of the special sections that may also be required. Figure 1.1 depicts a block diagram of a system containing some standard circuitry and the functions normally used.

As the figure shows, all components communicate via the system bus. The system bus is composed of the processor address, data, and control signals. The central processing unit (CPU) is the heart of the system, the master controller of all operations that can be performed. The terms CPU and microprocessor are interchangeable. The CPU executes

FIGURE 1.1 Standard block diagram of a microprocessor-based system

instructions that are stored in the memory section. For the sake of future expansion, the system bus is commonly made available to the outside world (through a special connector). Devices can then be added easily as the need arises. Commercial systems have predefined buses that accomplish this. All devices on the system bus must communicate with the processor, usually within a tightly controlled period of time. The timing section governs all system timing and thus is responsible for the proper operation of all system hardware. The timing section usually consists of a crystal oscillator and timing circuitry (counters designed to produce the desired frequencies) set up to operate the processor at its specified clock rate. Using a high-frequency crystal oscillator and dividing it down to a lower frequency provides for greater stability.

The CPU section consists of a microprocessor and the associated logic circuitry required to enable the CPU to communicate with the system bus. These logic elements may consist of data and address bus drivers, a bus controller to generate the correct control signals, and possibly a math coprocessor. **Math coprocessors** are actually microprocessors themselves; their instruction set consists mainly of simple instructions for transferring data, and complex instructions for performing a large variety of mathematical operations. Coprocessors perform these operations at very high clock speeds with a great deal of precision (80-bit results are common). In addition to the basic add/subtract/multiply/divide operations, coprocessors are capable of finding square roots, logarithms, a host of trigonometric functions, and more.

The actual microprocessor used depends on the complexity of the task that will be controlled or performed by the system. Simple tasks require nothing more complicated than an 8-bit CPU, which operates on 8 bits of data at a time. A computerized cash register would be a good example of this kind of system. Nothing more complicated than binary coded decimal (BCD) arithmetic—and possibly some record keeping—is needed. But for something as complex as a flight control computer for an aircraft or a digital guidance system for a missile, a more powerful 16- or 32-bit microprocessor must be used.

The memory section usually has two components; read-only memory (ROM) and random access memory (RAM). Some systems may be able to work properly without RAM, but all require at least a small amount of ROM. The ROM is included to provide the system with its intelligence, which is ordinarily needed at start-up (power-on) to configure or initialize the peripherals, and sometimes to help recover from a catastrophic system failure (such as an unexpected power failure). Some systems use the ROM program to download the main program into RAM from a larger, external system, such as a personal computer (PC) or a mainframe computer. In any event, provisions are usually made for adding additional ROM as the need arises.

There are three types of RAM. For small systems that do not process a great deal of data, the choice is static RAM. Static RAM is fast and easy to interface, but comes in small sizes (as little as 16 bytes per chip). Larger memory requirements are usually met by using dynamic RAM, a different form of memory that has high density (256K bits per chip or more), but that, unfortunately, requires numerous refreshing cycles to retain the stored data. Even so, dynamic RAM is the choice when large amounts of data must be stored, as in a system gathering seismic data at a volcano or receiving digitized video images from a satellite.

Both static and dynamic RAM lose their information when power is turned off, which could cause a problem in certain situations. Previous solutions involved adding battery backup circuitry to the system to keep the RAMs supplied with power during an outage. But batteries can fail, so a better method was needed; thus the invention of **nonvolatile memory** (NVM), which is memory that retains its information even when power is turned off. NVM comes in small sizes and therefore is used to store only the most important system variables in the event of a power outage.

Another type of storage media is the floppy disk or hard disk. Both types of disks provide the system with large amounts of storage for programs and data, although the data are accessed at a much slower rate than that of RAM or ROM. Floppy disks and hard disks also require complex hardware and software to operate and are not needed in many control applications.

With a microprocessor used in control applications, there will be times when the system must respond to special external circumstances. For example, a power failure on a computer-controlled assembly line requires immediate attention by the system, which must contain software designed to handle the unexpected event. The event actually *interrupts* the processor from its normal program execution to service the unexpected event. The system software is designed to handle the power-fail interrupt in a certain way and then return to the main program. An **interrupt**, then, is a useful way to grab the processor's attention, get it to perform a special task, and then resume execution from the point where it left off.

Not all types of interrupts are unexpected. Many are used to provide systems with useful features, such as real-time clocks, multitasking capability, and fast I/O operations.

The interrupt circuitry needed from system to system will vary depending on the application. A system used for keeping time has to use only a single interrupt line connected to a timing source. A more complex system, such as an assembly line controller that may need to monitor multiple sensors, switches, and other items, may require many different prioritized interrupts and would therefore need more complex interrupt circuitry.

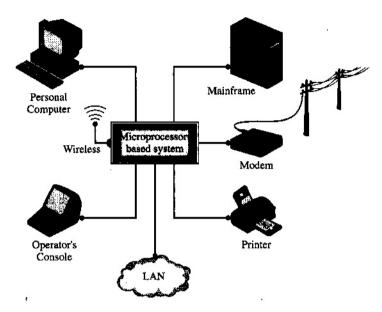

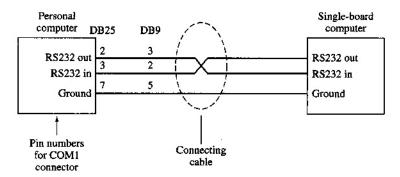

Some systems may require serial I/O for communication with an operator's console or with a host computer. In serial communication, data is transmitted one bit at a time between devices. In Figure 1.2, we see how a small system might communicate with other devices or systems via serial communication. Although this type of communication is slower than parallel communication, it has the advantage of simplicity: only two wires (for

FIGURE 1.2 Serial communication possibilities in a small system

receive and transmit) plus a ground are needed. Serial communication is easily adapted for use in fiber-optic cables. Parallel I/O, on the other hand, requires more lines (at least eight), but has the advantage of being very fast. A special parallel operation called **direct memory access (DMA)** is used to transfer data from a hard disk to a microcomputer's memory. Other uses for parallel I/O involve reading switch information, controlling indicator lights, and transferring data to A/D and D/A converters and other types of parallel devices.

All of these sections have their uses in a microprocessor-based system. Whether they are actually used depends on the designer and the application.

#### 1.4 MICROPROCESSOR OPERATION

No matter how complex microprocessors become, they will still follow the same pattern of operations during program execution: endless fetch, decode, and execute cycles. During the fetch cycle, the processor loads an instruction from memory into its internal instruction register. Some advanced microprocessors load more than one instruction into a special buffer to decrease program execution time. The idea is that while the microprocessor is decoding the current instruction, other instructions can be read from memory into the instruction cache, a special type of internal high-speed memory. In this fashion, the microprocessor performs two jobs at once, thus saving time.

During the decode cycle, the microprocessor determines what type of instruction has been fetched. Information from this cycle is then passed to the execute cycle. To complete

Determine what type of

instruction was fetched.

Execute instruction.

If necessary, write results

This process repeats until power is turned off or the processor is halted.

memory.

to memory.

1. If necessary, read data from

Figure 1.3 Microprocessor operation

Reset

Start here at power-on or when a reset signal is received.

1. Output instruction address onto address bus.

2. Read instruction pattern from memory onto data bus.

3. Increment instruction pointer (program counter).

the instruction, the execute cycle may need to read more data from memory or write results to memory. This process is illustrated in Figure 1.3.

Decode

Execute

While these cycles are proceeding, the microprocessor is also paying attention to other details. If an interrupt signal arrives during execution of an instruction, the processor latches onto the request, holding off on interrupt processing until the current instruction finishes execution. The processor also monitors other signals such as WAIT, HOLD, or READY inputs. These are usually included in the architecture of the microprocessor so that slow devices, such as memories, can communicate with the faster processor without loss of data.

Most microprocessors also include a set of control signals that allows external circuitry to take over the system bus. In a system where multiple processors share the same memory and devices, these types of control signals are necessary to resolve bus contention (two or more processors needing the system bus at the same time). Multiple-processor systems are becoming more popular now as we continue to strive toward faster execution of our programs. Parallel processing is a term often used to describe multiple-processor systems and their associated software.

Special devices called **microcontrollers** are often used in simple control systems because of their many features. Microcontrollers are actually souped-up microprocessors with built-in features such as RAM, ROM, interval timers, parallel I/O ports, and even A/D converters. Microcontrollers are not used for large systems, however, because of their small memory addressing capability and limited processing speed. Unfortunately, we have yet to get everything we want on a single chip!

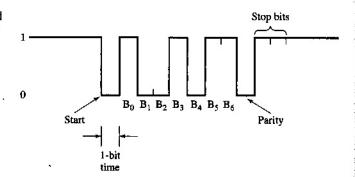

#### 1.5 HARDWARE/SOFTWARE REQUIREMENTS

We saw earlier that it is necessary to have at least some ROM in a system to take care of peripheral initialization. What type of initialization is required by the peripherals? The serial device must have its baud rate (communication speed), parity, and number of data and stop bits programmed. Parallel devices must be configured because most of them allow the direction (input or output) of their I/O lines to be programmed in many different ways. It is then necessary to set the direction of these I/O lines when power is first applied. For a system containing a D/A converter, it may be important to output an initial value required by the external hardware. Because we can never assume that correct conditions exist at power-on, the microprocessor is responsible for establishing them.

Suppose a certain system contains a video display controller. Start-up software must select the proper screen format and initialize the video memory so that an intelligent picture (possibly a menu) is generated on the screen of the display. If the system uses lightemitting diode (LED) displays or alphanumeric displays for output, they must be properly set as well. High-reliability systems may require that memory be tested at power-on. While this adds to the complexity of the start-up software and the time required for initialization, it is a good practice to follow. Bad memory devices will certainly cause a great deal of trouble if they are not identified.

Other systems may employ a special circuit called a watchdog monitor. The circuit operates like this: during normal program execution, the watchdog monitor is disabled. Should the program ever from its proper course, the monitor will automatically reset the system. A simple way to make a watchdog monitor is to use a binary counter, clocked by a known frequency. If the counter is allowed to increment up to a certain value, the processor is automatically reset. The software's job, if it is working correctly, is to make sure that the counter never reaches this count. A few simple logic gates can be used to clear the counter under microprocessor control, possibly whenever the CPU examines a certain memory location.

For flexibility, the system may have been designed to download its main program from a host system. If this is the case, the system software will be responsible for knowing how to communicate with the host and place the new program into the proper memory locations. To guarantee that the correct program is loaded, the software should also perform a running test on the incoming data, requesting the host to retransmit portions of the data whenever it detects an error.

Sometimes preparing for a power-down is as important as doing the start-up initialization. A power supply will quite often supply voltage in the correct operating range for a few milliseconds after the loss of AC power. During these few milliseconds the processor must execute the shutdown code, saving important system data in nonvolatile RAM or doing whatever is necessary for a proper shutdown. If the system data can be preserved, it may be possible to continue normal execution when power is restored.

For systems that will be expanded in the future, the system bus must be made available to the outside world. To protect the internal system hardware, all signals must be properly buffered. This involves using tri-state buffers or similar devices to isolate the internal system bus from the bus available to the external devices. Sometimes optoisolators are used to completely separate the internal system signals from the external ones. The only connection in optoisolators is a beam of light, which makes them ideal when electrical isolation is required.

FIGURE 1.4 Expanded block diagram of a microprocessor-based system

Figure 1.4 sums up all of these concepts with an expanded block diagram of a microprocessor-based control system. Notice once again that all devices in the system communicate with the CPU via the system bus.

#### 1.6 THE PERSONAL COMPUTER

All of the material in this chapter, up to this point, has dealt with general microprocessor-based systems. In this section, we will see how a specific microprocessor-based system, the PC, uses many of the hardware features already described. Although the PC has been

around for many years and has evolved into a powerful machine containing very advanced technology, it began as a much simpler machine constructed around the 8/16-bit Intel 8088 microprocessor. The 8088 came out in the late 1970s and offered a higher level of computing power than the 8-bit processors of the time. When IBM® chose the 8088 for use in its new PC, it paved the way for worldwide acceptance of the new processor. Many companies began copying the architecture of the PC and offered their own compatible 8088-based computer systems. Thus began the PC market.

One reason the PC market grew as fast as it did was due to the usefulness of the features the PC offered. The initial PC contained a keyboard for entering commands and data, a monochrome video display for viewing text and simple graphics, one or two floppy disk drives for storing information and running programs, and a memory large enough for many useful applications. It also came equipped with a software program called DOS, for Disk Operating System, which made it possible to access files on the disk drives and run programs with the use of simple commands.

Most of the electronics within the PC were contained on a single printed circuit board called the **motherboard**. Memory chips, timing circuitry, interrupt logic, the 8088 microprocessor, and other hardware all resided on the motherboard. Included were a number of expansion slots, plastic connectors with metal fingers into which other circuit boards could be plugged. The PC's system bus was wired to each expansion slot, so any card plugged into an expansion slot had the power of the entire machine available to it. Expansion cards were used to add new features to the basic machine, such as a color video display, a hard disk, or additional memory. Today, there are hundreds of different expansion cards available. A small sample of them shows the wide variety of hardware applications:

Modem/Fax

LAN controller

Data acquisition

Sound/speech synthesis

High-resolution color graphics

Image processing

CD-ROM drive

Hand-held and flatbed scanner

Serial/parallel I/O

Clearly, with the right number and type of expansion cards, the PC can be configured to do just about anything. For our purposes, we will concentrate on the hardware that comes with a base machine, with a few add-ons, namely the hard disk and color-display cards.

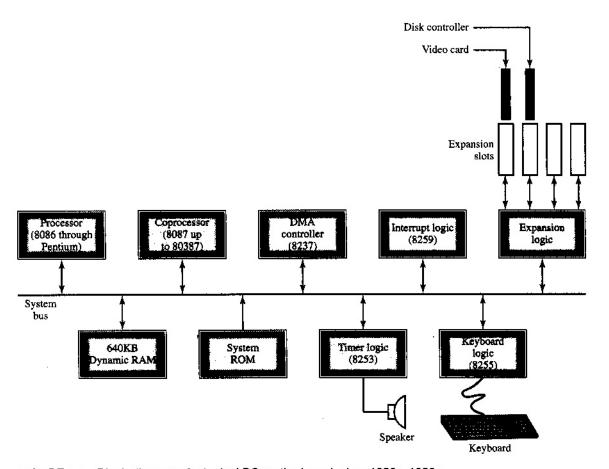

Let us now take a detailed look at the inside of the personal computer. Figure 1.5 is the block diagram for a typical PC motherboard from the early days of the PC. As shown, all communication is through the system bus. The microprocessor may be an 8088 (as found on the original PC), or one of the newer 32-bit processors from Intel, such as the 80386<sup>TM</sup> or 80486<sup>TM</sup>. A nice feature of the advanced Intel microprocessors is that they all execute programs written for the 8088. So, even if your machine is new, all of the software presented in this textbook will run on it.

If a motherboard contains an 8088 microprocessor, there is usually a socket provided for an additional chip, the 8087 Floating-Point Coprocessor. This device is capable of performing mathematical calculations much faster than the 8088 and is designed to work in parallel with the processor. Motherboards based on the 80486 do not contain this socket because the coprocessor is built into the processor itself.

FIGURE 1.5 Block diagram of a typical PC motherboard, circa 1980s-1990s

For high-speed data transfers involving memory, the motherboard contains an 8237<sup>TM</sup> DMA Controller. This device can be easily programmed to move large chunks of data without assistance from the processor.

The PC has many features that require the use of the interrupt system. An 8259<sup>TM</sup> Programmable Interrupt Controller is included to handle the interrupts generated by the PC's time-of-day clock, keyboard, serial and parallel I/O devices, and disk drives.

The motherboard contains a small amount of ROM as well. This ROM is referred to as system ROM and is used to control the PC when it is turned on. The system ROM is responsible for checking and initializing all peripherals and devices on the motherboard and for starting up the disk drive to load DOS.

As mentioned before, the PC maintains a time-of-day clock. This clock is a combination of software and hardware. A special timing device, the 8253<sup>TM</sup> Programmable Interval Timer, is used to generate timing pulses at regular intervals. These pulses interact with the interrupt logic and DOS to simulate the passage of time. The 8253 also controls the PC's speaker. With proper programming, it is possible to make the speaker beep and generate other sounds.

A parallel I/O device, the 8255 Programmable Peripheral Interface, is used to monitor and read the PC's keyboard and motherboard option switches.

Finally, expansion logic is used to drive the system bus signals on the expansion slots. This makes it possible for circuitry on an expansion card to access every device on the

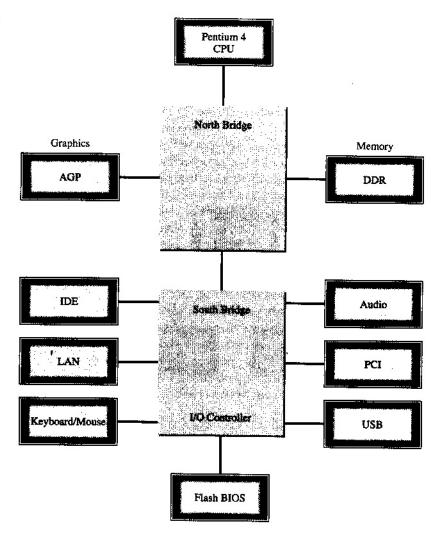

**FIGURE 1.6** Chipset-based motherboard in use today

motherboard. As processors evolved, so did motherboard technology. Figure 1.6 shows the block diagram of a typical motherboard used today. Each microprocessor now has an associated chipset on the motherboard to interface it with the motherboard components. The chipset consists of a pair of powerful integrated circuits that essentially act as communication hubs. The North Bridge controls high-speed data transfers between the CPU, memory, and the graphics system. Slower I/O is accomplished through the South Bridge, an integrated I/O controller that provides all the motherboard I/O needs in a single package.

We do not have to know a great deal about the hardware just described to write programs for the personal computer.

#### 1.7 DEVELOPING SOFTWARE FOR THE PERSONAL COMPUTER

To get the most use out of the power of the PC, it is necessary to understand how to control and use the hardware on the motherboard and the software capabilities of the processor. We will explore the software architecture of the 80x86 family in great detail in the

following chapters, first by examining the instruction set and then by looking at programming examples. What we will see is that the 80x86 processors speak a different language than we do.

#### Machine Language vs. Assembly Language

Our language is one of words and phrases. The 80x86 language is a string of 1s and 0s. For example, the instruction

```

ADD AX, BX

```

contains a word, ADD, that means something to us. Apparently, we are adding AX and BX together, whatever they are. So, even though we might be unfamiliar with the 80x86 instruction set, the instruction ADD AX, BX means something to us.

If we were instead given the binary string

```

0000 0001 1101 1000

```

or the hexadecimal equivalent

```

01 D8

```

and asked its meaning, we might be hard-pressed to come up with anything. We associate more meaning with ADD AX, BX than we do with 01 D8, which is the way the instruction is actually represented. All programs for the 80x86 will simply be long strings of binary numbers.

Because of the processor's internal decoders, different binary patterns represent different instructions. Here are a few examples to illustrate this point:

```

01 D8

ADD

AX, BX

; add BX to AX, result in AX

29 D8

; subtract BX from AX, result in AX

SHE

AX, BX

AX,BX

21 D8

;AX equals AX AND BX

AND

40

INC

AX

;add 1 to AX

BX

; subtract 1 from BX

4 B

DEC

8B C3

MOV

AX,BX

; copy BX into AX

```

Can you guess the meaning of each instruction just by reading it? Do the hexadecimal codes for each instruction mean anything to you? What we see here is the difference between machine language and assembly language. The machine language for each instruction is represented by the hexadecimal codes. This is the binary language of the machine. The assembly language is represented by the word-like terms that mean something to us. Putting groups of these word-like instructions together is how a program is constructed. In the next few sections, we will see how an assembly language program is written, converted into machine language, and executed.

#### NUMOFF: Our First Machine Language Program

When the personal computer is first turned on, instructions in the start-up software turn the NUM-LOCK indicator on. This indicator is located near the NUM-LOCK button on the keyboard. Pushing NUM-LOCK manually every time the PC is turned on (or even rebooted) is annoying. Luckily, there is a single bit stored in a specific memory location used by DOS that controls the state of the NUM-LOCK indicator. We are about to see that it is possible to write an 80x86 program to manipulate the NUM-LOCK status bit.

#### One Way to Create an Executable Program

One way to create a working program would involve these steps:

**Step 1:** Using a PC-based word processor, enter the following text file exactly as you see it. Save the file under the name of NUMOFF.ASM.

```

: NUMOFF. ASM: Turn NUM-LOCK indicator off.

;

.MODEL $MALL

.STACK

.CODE

.STARTUP

MOV

AX,40H

;set AX to 0040H

MOV

DS, AX

;load data segment with 0040H

MOV

SI,17H

:load SI with 0017H

BYTE PTR [SI], ODFH

AND

;clear NUM-LOCK bit

.EXIT

END

```

The twelve lines of code constitute a source file, the starting point of any 80x86-based program. Thus, NUMOFF.ASM is a source file.

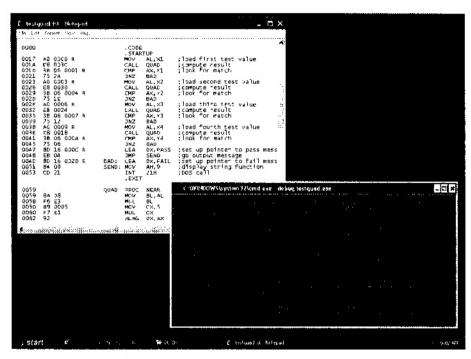

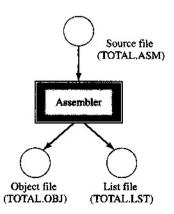

To convert NUMOFF.ASM into a group of hexadecimal bytes that represents the corresponding machine language, we make use of two additional programs: ML and LINK. ML is an assembler, a program that takes a source file as input and determines the machine language for each source statement. ML creates two additional files. These are the *list* and *object* files. The list file contains all of the text from the source file, plus additional information, as we will soon see. The object file contains only the machine language.

Step 2: To assemble NUMOFF.ASM, enter the following command at the DOS prompt:

```

ML /c /Fl NUMOFF.ASM <cr>

```

where <cr> indicates a carriage return. Note: This command does not work until you install the assembler software. This command instructs ML to assemble NUMOFF.ASM and create NUMOFF.LST (the list file) and NUMOFF.OBJ (the object file). The list file created by ML looks like this:

```

; NUMOFF. ASM: Turn NUM-LOCK indicator off.

.MODEL SMALL

.STACK

0000

.CODE

.STARTUP

0017 B8 0040

MOV

AX,40H

;set AX to 0040H

DS, AX

001A 8E D8

MOV

;load data segment with 0040H

001C BE 0017

MOV

SI,17H

;load SI with 0017H

001F 80 24 DF

AND

BYTE PTR [SI], ODFH ; clear NUM-LOCK bit

EXIT

END

```

Here, it is obvious that ML has determined the machine language for each source statement. The first column is the set of memory locations where the instructions are stored. The second column is the group of machine language bytes that represent the actual 80x86 instructions.

Step 3: To make the object file executable, we run the LINK program, which converts NUMOFF.OBJ into NUMOFF.EXE. The DOS command to do this is:

```

LINK NUMOFF: < cr>

```

Now we have our first working 80x86 program, NUMOFF.EXE! To test it, press the NUM-LOCK button on the PC's keyboard until the NUM-LOCK light goes on. Then execute NUMOFF.EXE by entering:

```

NUMOFF.EXE<cr>

```

at the DOS prompt. The NUM-LOCK light should go off. This is what NUMOFF.EXE does. This program may have no effect in Windows XP and other environments, due to increased OS control over the hardware. However, it is an example of how a few simple instructions can do something useful.

Many of the programs in later chapters will be assembled and linked in this fashion.

#### Generating Machine Code with DEBUG

An alternate technique for generating and executing machine code is through the use of the DEBUG program. Unlike the ML assembler program, DEBUG comes with the DOS and Windows operating systems. Let us briefly look at how DEBUG can be used to perform the same task as the NUMOFF.EXE program. We'll take a more detailed look at DEBUG later.

From the DOS prompt, start up DEBUG with:

```

DEBUG<cr>

```

You will get a minus sign (-) as a prompt, which helps to distinguish the DEBUG environment from the DOS environment.

Now enter all of the following text shown in bold. You will almost surely see different addresses on your machine than those that appear here, but this will not affect what we are trying to do.

```

-a<cr>

7F2D:0100 mov ax,40<cr>

7F2D:0103 mov ds,ax<cr>

7F2D:0105 mov si,17<cr>

7F2D:0108 and byte ptr [si],df<cr>

7F2D:0108 </r>

```

The <cr> on the last line gets you out of the "a" mode. Because "a" stands for assemble, DEBUG has assembled each statement entered by the user and placed the corresponding machine code into memory. This is indicated by the way addresses are incrementing in the address field (0100 to 0103 to 0105, etc.).

Now push the NUM-LOCK button on your keyboard so that the NUM-LOCK indicator is on. To execute the program statement by statement, enter a single "t" at DEBUG's prompt:

```

-t<cr>

```

This is the *trace* command, and it is used to single-step through an 80x86 program. Each time you enter "t," DEBUG will execute one instruction of your program and display the results.

If you hit "t" three more times, you should see the NUM-LOCK indicator go off. This completes the program. To exit from DEBUG back to DOS, enter:

-q<cr>

This shows that DEBUG is also a useful way of executing machine language programs. We will write and execute a number of programs this way and learn much more about how DEBUG works. We will also look at ways to develop programs specifically for protected-mode Windows and for Linux systems.

**Programming Exercise 1.1:** Can you think of a way to do the opposite of NUMOFF? That is, can you change NUMOFF so that it turns NUM-LOCK on?

Hint: Use an OR operation.

**Programming Exercise 1.2:** Can you think of a way to toggle the NUM-LOCK indicator? This would cause NUM-LOCK to alternate between on and off.

Hint: Use an XOR operation.

#### 1.8 TROUBLESHOOTING TECHNIQUES

You may think it premature to begin discussing troubleshooting techniques, when we have been exposed to so little of the 80x86 family architecture. Even so, we have already seen a number of places where errors can occur, and it would be worthwhile to discuss them. For example, the NUMOFF.ASM source file could have contained one or more typographical errors, such as a misspelled instruction (MVO versus MOV), or a missing comma, or a comma where a semicolon was expected. Generally, when errors such as these are present in a source file, the assembler will report them with a brief error message.

Even if the source file does not have any typographical errors, we could still run into trouble. We could enter the command to invoke ML or DEBUG incorrectly, or not use the correct options.

When the source file correctly assembles and links, and an executable program has been created, there is still the possibility of a *run-time* error in the program. Run-time errors are typically caused by incorrect sequences of instructions and incomplete or faulty logical thinking.

To avoid a loss of time and effort, it is good to keep these common stumbling blocks in mind. Paying attention to the details will really pay off, as you learn to create a working program with a minimum of time and effort.

#### SUMMARY

In this chapter, we have examined the operation of microprocessor-based systems. We saw that the complexity of the hardware, and thus of the software, is a function of the type of application. Through the use of many different types of peripherals, such as parallel and serial devices, analog-to-digital converters, and others, a system can be tailored to perform

STUDY QUESTIONS 19

almost any job. We also reviewed the basic fetch, decode, and execute cycle of a microprocessor, and examined the other duties the CPU performs, one of which was interrupt handling.

We also covered the initialization requirements of peripherals used in a microprocessor-based system, and why it is necessary to perform initialization in the first place. Other types of hardware and software requirements were also examined, such as the use of a watchdog monitor and a nonvolatile memory.

Four different generations of computers were presented and their differences highlighted. Current computing trends dealing with parallel processing and artificial intelligence were also introduced.

This was followed by an introduction to the motherboard hardware of a typical personal computer. Any *compatible* PC must use the same hardware. Because software is needed to control the hardware, we finished with a quick look at two techniques for creating and executing machine language programs. The first technique used ML and LINK, and the second technique used DEBUG. Both methods will be covered in detail in following chapters.

#### STUDY QUESTIONS

- 1. Make a list of ten additional products containing microprocessors that we use every day.

- 2. (a) The cycle time of a microprocessor is the time for one complete clock cycle. For example, if the clock frequency of a microprocessor is 2 million cycles per second (2 MHz), then each cycle takes 500 ns (500 billionths of a second). Compare the cycle time of a microprocessor running at 2 MHz with one running at 50 MHz, 500 MHz, and 2 GHz.

- (b) If a certain 80x86 instruction requires four clock cycles to execute, how long does the instruction take to execute if the processor clock speed is 25 MHz? Repeat for a clock speed of 800 MHz.

- 3. Speculate on the uses for timing signals in the serial I/O, memory, and interrupt sections.

- 4. Why do math coprocessors enhance the capabilities of an ordinary CPU?

- 5. Draw a block diagram for a computerized cash register. The hardware should include a numerical display, a keyboard, and a compact printer.

- 6. What kind of initialization software would be required for the cash register in Question 5?

- 7. What would be the difference in system RAM requirements for two different cash registers, one without record keeping and one with?

- 8. What type of information should be stored in NVM during a power failure in a system designed to control navigation in an aircraft?

- 9. What types of interrupts may be required in a control system designed to monitor all doors, windows, and elevators in an office complex?

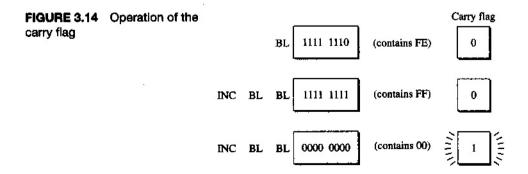

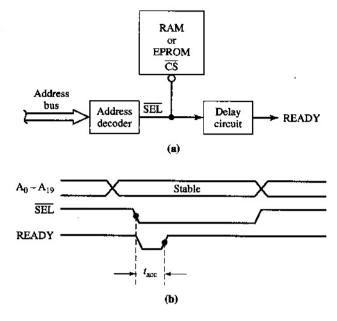

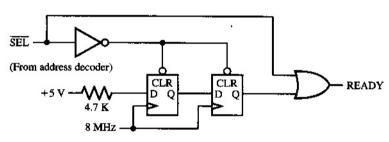

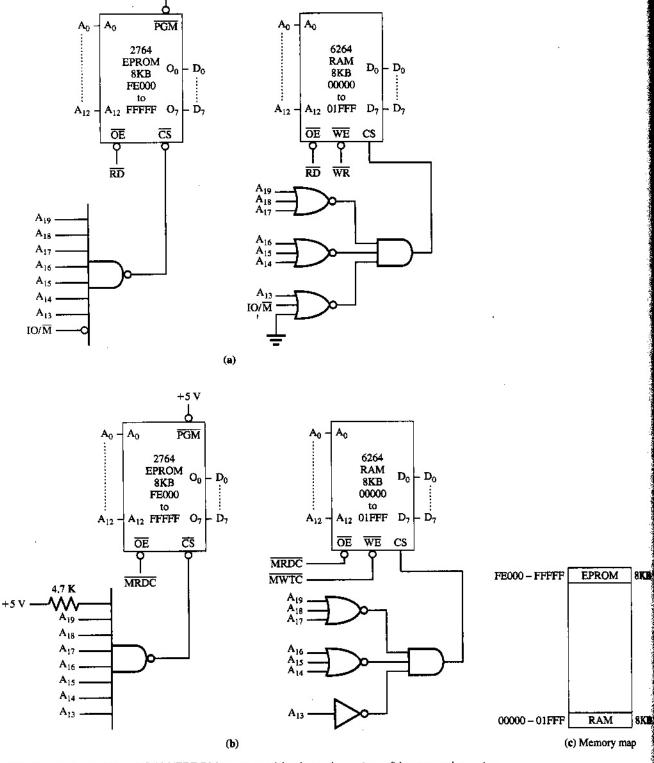

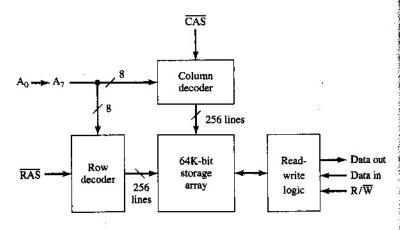

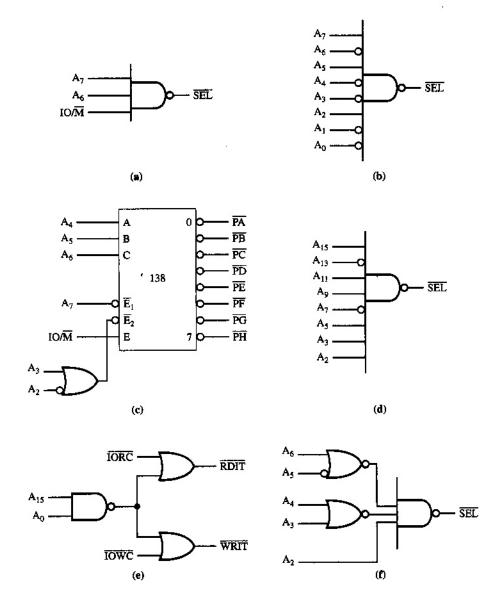

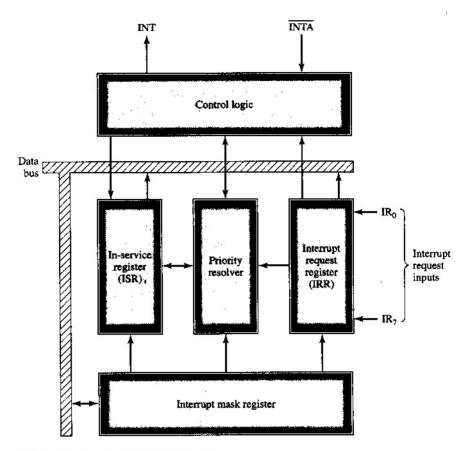

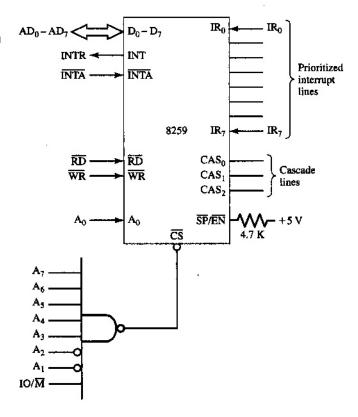

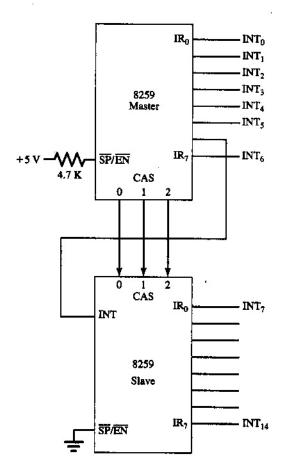

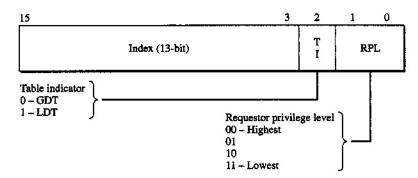

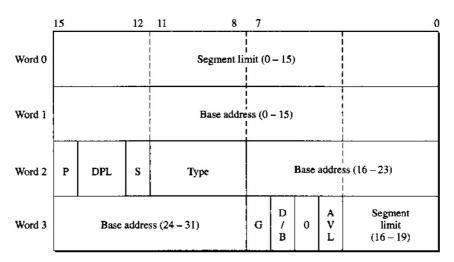

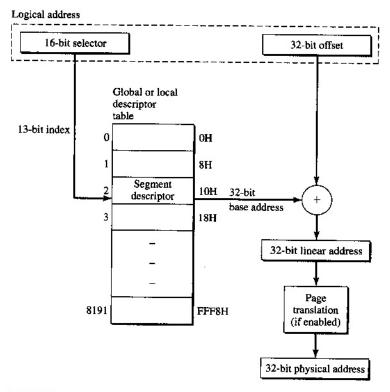

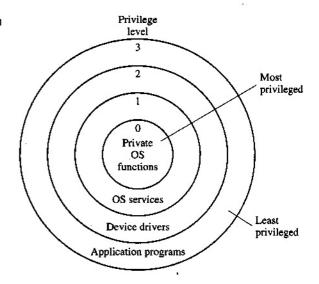

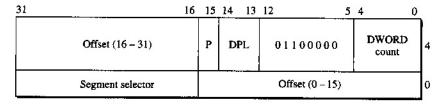

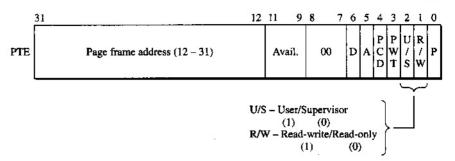

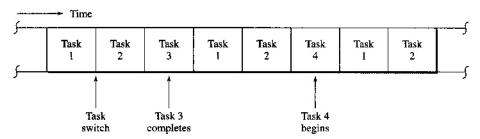

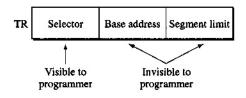

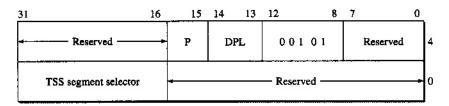

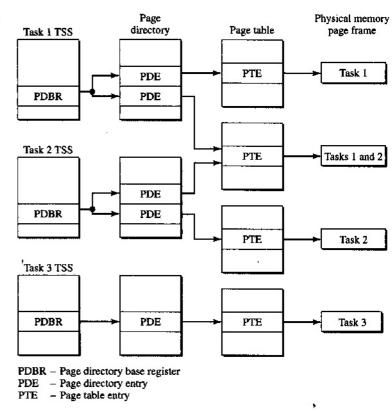

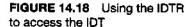

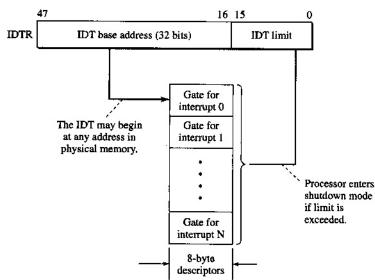

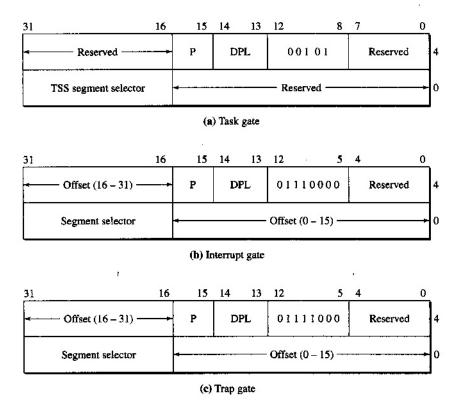

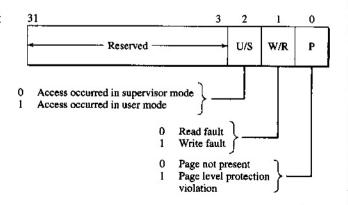

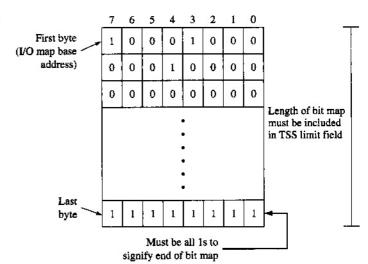

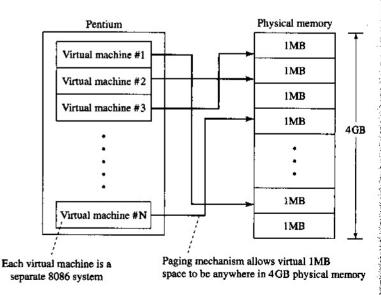

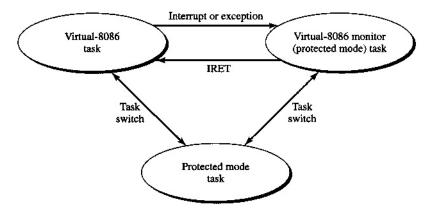

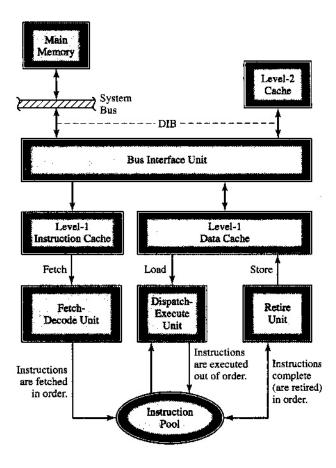

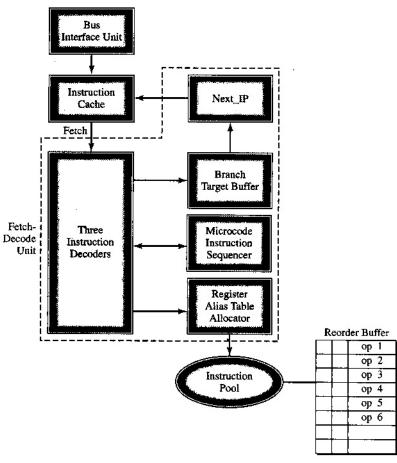

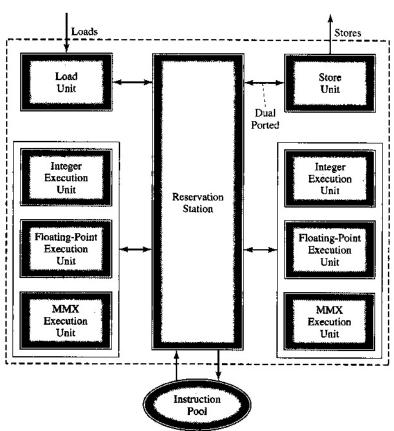

- 10. Name some advantages of downloading the main program into a microprocessor-based system. Are there any disadvantages?