# Building a Programmable Logic Controller with a PIC16F648A Microcontroller

### **Murat Uzam**

### Building a Programmable Logic Controller with a PIC16F648A Microcontroller

## Building a Programmable Logic Controller with a PIC16F648A Microcontroller

### **Murat Uzam**

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2014 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20130710

International Standard Book Number-13: 978-1-4665-8986-5 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

To my parents and family

who love and support me

and

to my teachers and students

who enriched my knowledge

### Contents

| Pr | etace  |          |                                                       | X111 |

|----|--------|----------|-------------------------------------------------------|------|

| Αc | knowl  | edgmen   | its                                                   | xv   |

| Ва | ckgrou | ınd and  | Use of the Book                                       | xvii |

| Αŀ | out th | e Autho  | rλ                                                    | xiii |

|    |        |          |                                                       |      |

| 1  | Hard   | lware of | f the PIC16F648A-Based PLC                            | 1    |

|    |        |          |                                                       |      |

| 2  |        |          | are                                                   |      |

|    | 2.1    |          | oftware Structure                                     |      |

|    |        | 2.1.1    | Variable Definitions                                  |      |

|    |        | 2.1.2    | Macro HC165                                           |      |

|    |        | 2.1.3    | Macro HC595                                           | 21   |

|    | 2.2    |          | ation of Contact Bouncing Problem in the              |      |

|    |        | PIC16F   | 648A-Based PLC                                        | 22   |

|    |        | 2.2.1    | Contact Bouncing Problem                              |      |

|    |        | 2.2.2    | Understanding a Generic Single I/O Contact Debouncer. |      |

|    |        | 2.2.3    | Debouncer Macros dbncr0 and dbncr1                    |      |

|    | 2.3    |          | Macros of the PIC16F648A-Based PLC                    |      |

|    |        | 2.3.1    | Macro initialize                                      |      |

|    |        | 2.3.2    | Macro get_inputs                                      |      |

|    |        | 2.3.3    | Macro send_outputs                                    |      |

|    | 2.4    | Examp    | ole Program                                           | 34   |

|    |        |          |                                                       |      |

| 3  |        |          | Relay-Based Macros                                    |      |

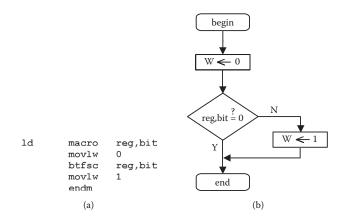

|    | 3.1    |          | ld (load)                                             |      |

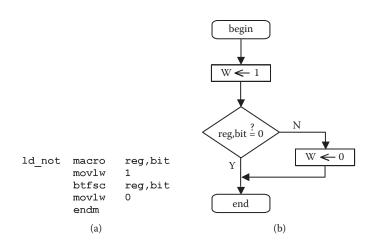

|    | 3.2    |          | ld_not (load not)                                     |      |

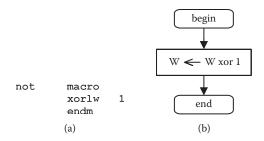

|    | 3.3    |          | not                                                   |      |

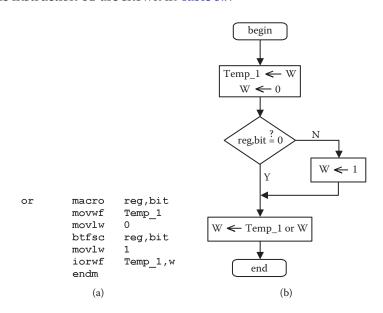

|    | 3.4    |          | or                                                    |      |

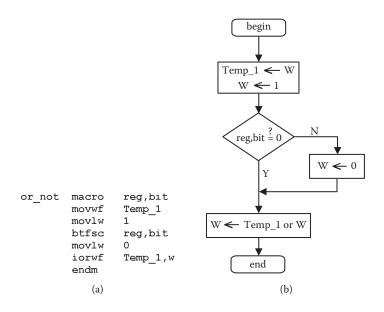

|    | 3.5    |          | or_not                                                |      |

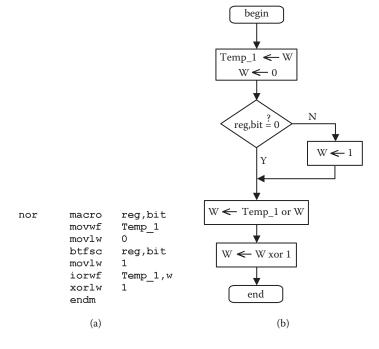

|    | 3.6    |          | nor                                                   |      |

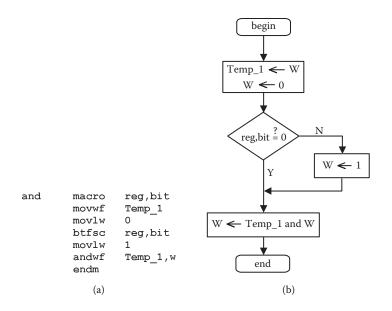

|    | 3.7    |          | and                                                   |      |

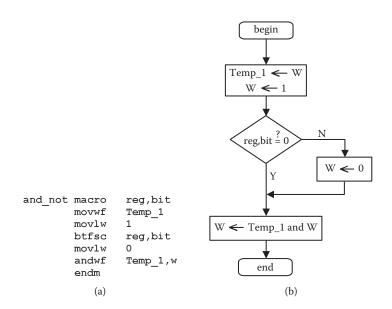

|    | 3.8    |          | and_not                                               |      |

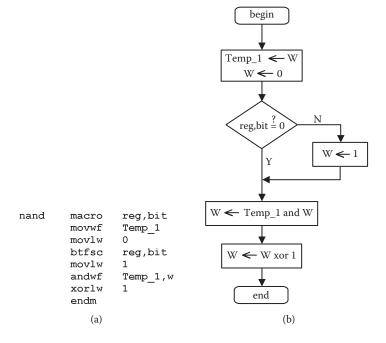

|    | 3.9    |          | nand                                                  |      |

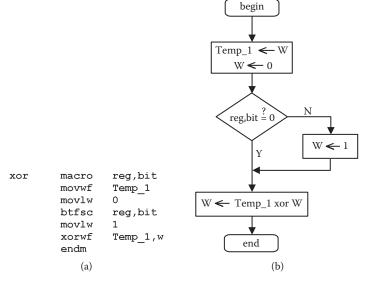

|    | 3.10   |          | xor                                                   |      |

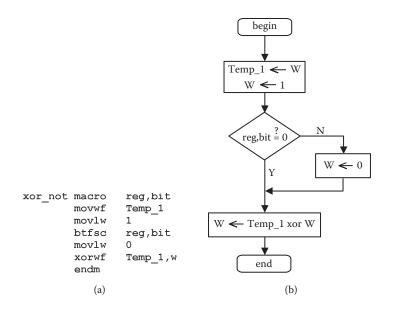

|    | 3.11   |          | xor_not                                               |      |

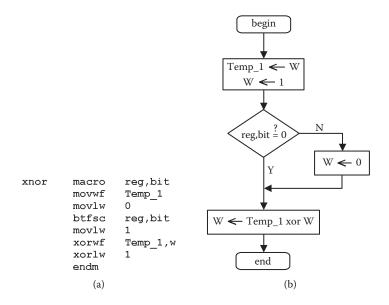

|    | 3.12   |          | xnor                                                  |      |

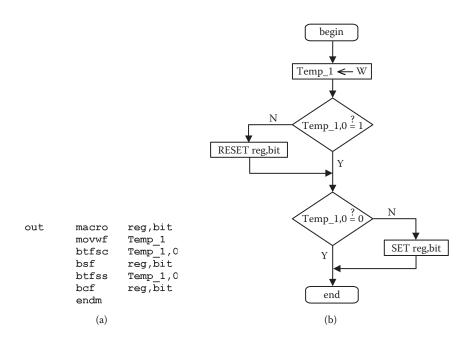

|    | 3.13   |          | out                                                   |      |

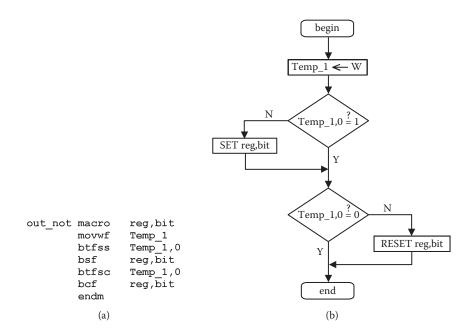

|    | 3.14   |          | out_not                                               |      |

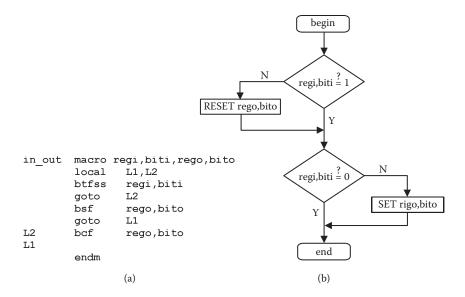

|    | 3.15   | Macro    | in_out                                                | 54   |

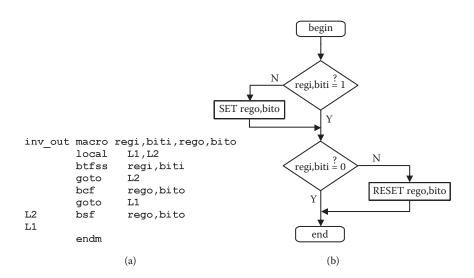

|    | 3.16   | Macro    | inv out                                               | 56   |

viii Contents

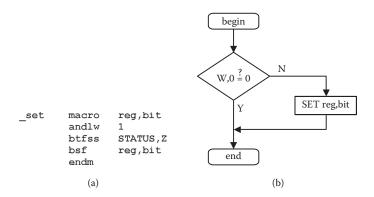

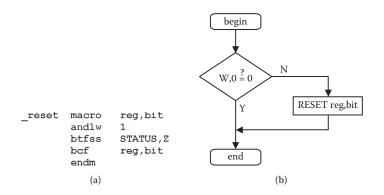

|   | 3.17  | Macro _set                                         | 57  |

|---|-------|----------------------------------------------------|-----|

|   | 3.18  | Macro reset                                        |     |

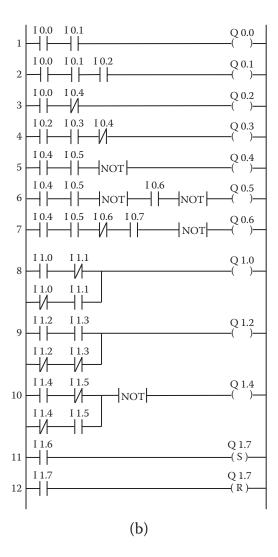

|   | 3.19  | Examples for Contact and Relay-Based Macros        |     |

| 4 | Flip- | Flop Macros                                        | 67  |

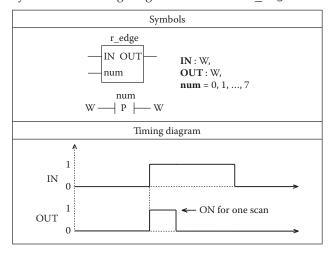

|   | 4.1   | Macro r_edge (Rising Edge Detector)                | 68  |

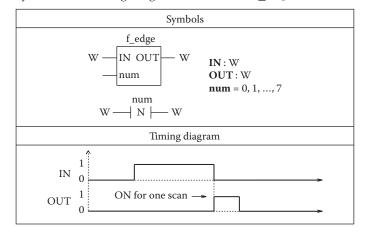

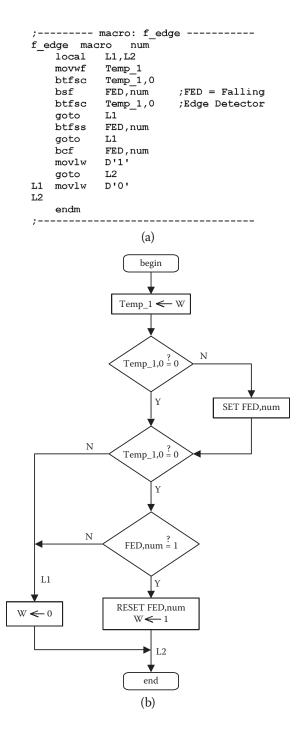

|   | 4.2   | Macro f_edge (Falling Edge Detector)               | 70  |

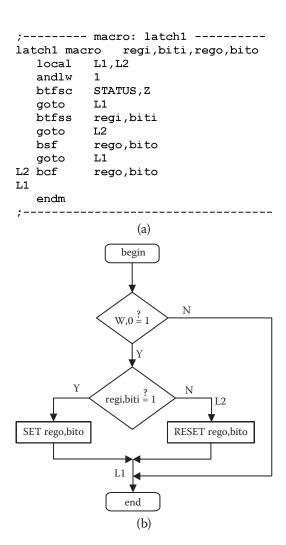

|   | 4.3   | Macro latch1 (D Latch with Active High Enable)     | 72  |

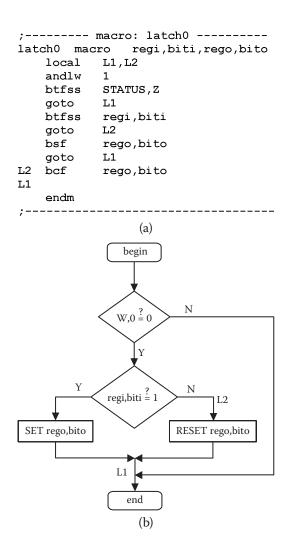

|   | 4.4   | Macro latch0 (D Latch with Active Low Enable)      | 72  |

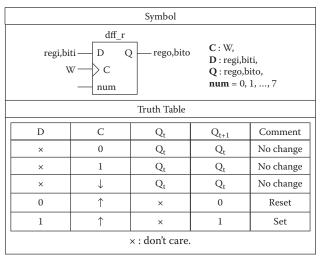

|   | 4.5   | Macro dff_r (Rising Edge Triggered D Flip-Flop)    |     |

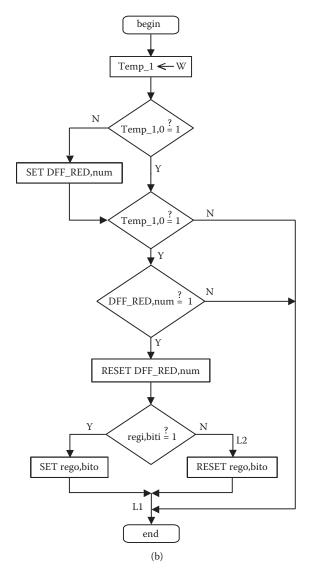

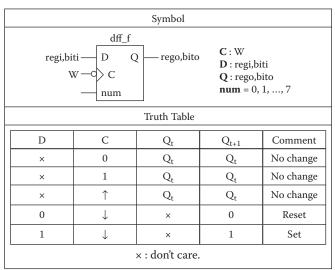

|   | 4.6   | Macro dff_f (Falling Edge Triggered D Flip-Flop)   | 77  |

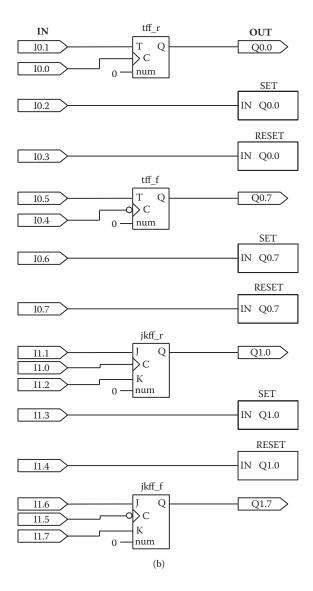

|   | 4.7   | Macro tff_r (Rising Edge Triggered T Flip-Flop)    | 80  |

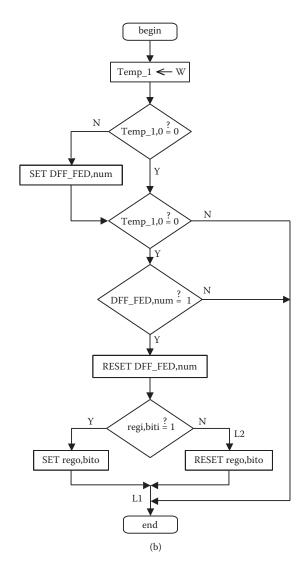

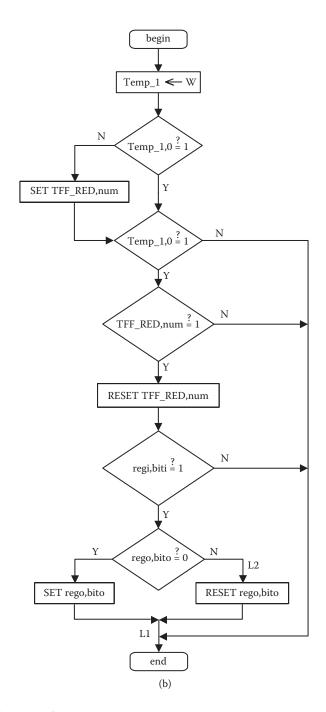

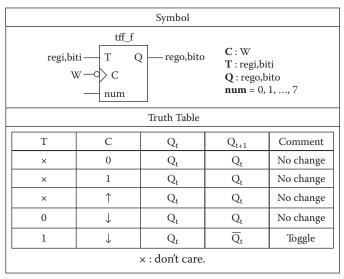

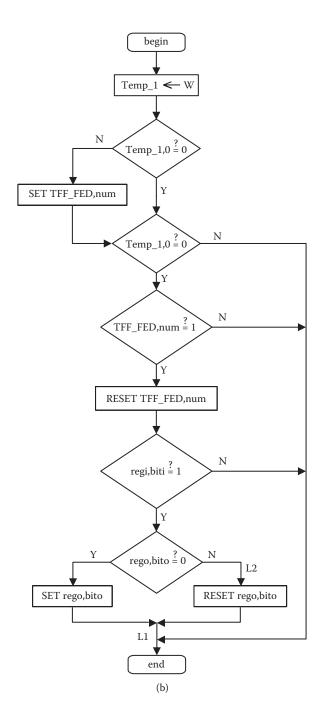

|   | 4.8   | Macro tff_f (Falling Edge Triggered T Flip-Flop)   | 82  |

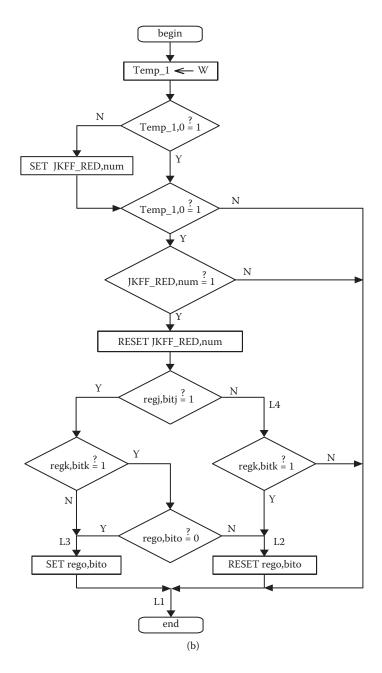

|   | 4.9   | Macro jkff_r (Rising Edge Triggered JK Flip-Flop)  | 82  |

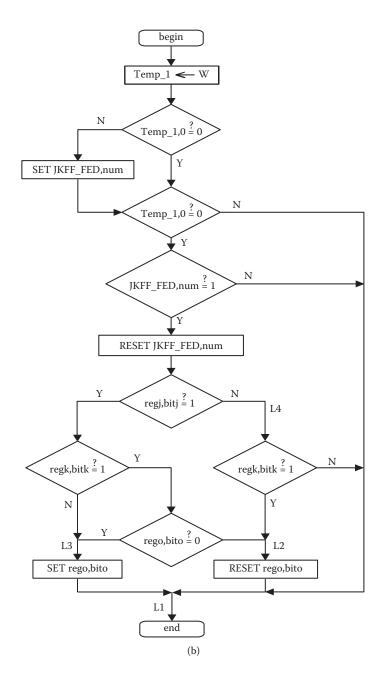

|   | 4.10  | Macro jkff_f (Falling Edge Triggered JK Flip-Flop) |     |

|   | 4.11  | Examples for Flip-Flop Macros                      | 88  |

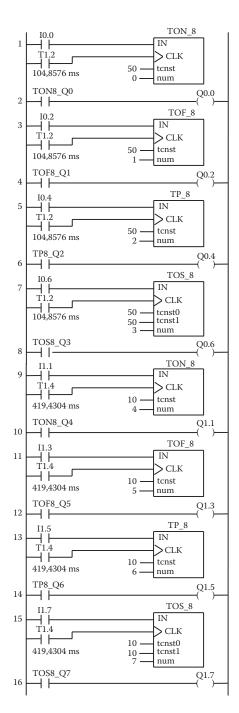

| 5 | Time  | er Macros                                          | 97  |

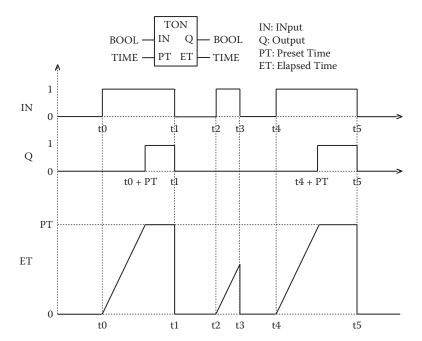

|   | 5.1   | On-Delay Timer (TON)                               |     |

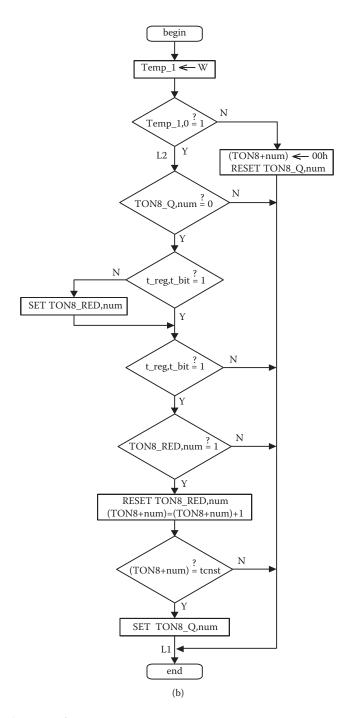

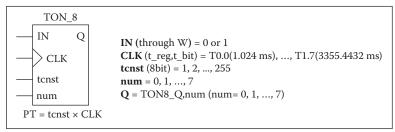

|   | 5.2   | Macro TON_8 (8-Bit On-Delay Timer)                 | 98  |

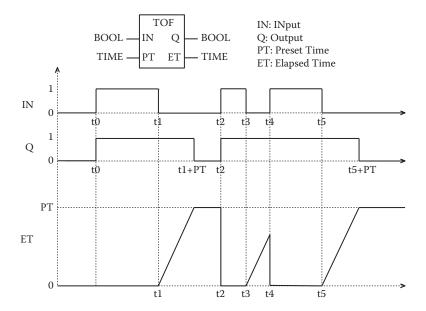

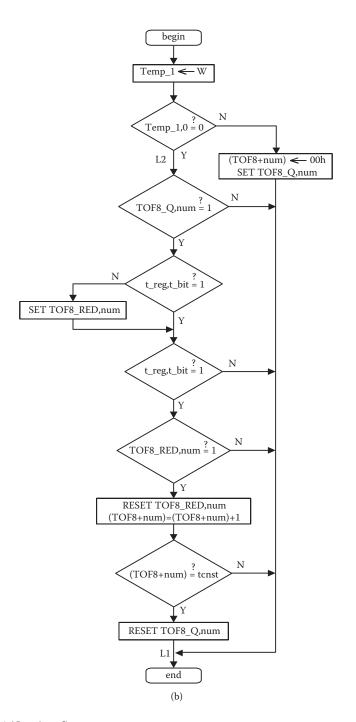

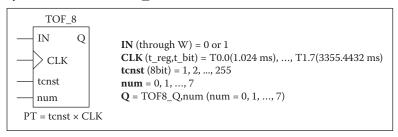

|   | 5.3   | Off-Delay Timer (TOF)                              |     |

|   | 5.4   | Macro TOF_8 (8-Bit Off-Delay Timer)                | 105 |

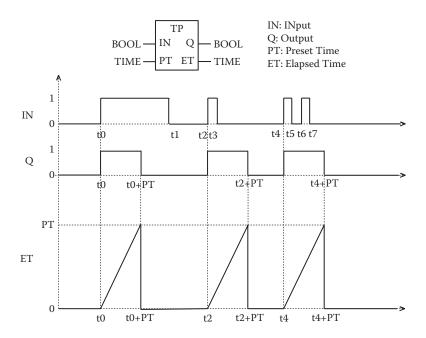

|   | 5.5   | Pulse Timer (TP)                                   |     |

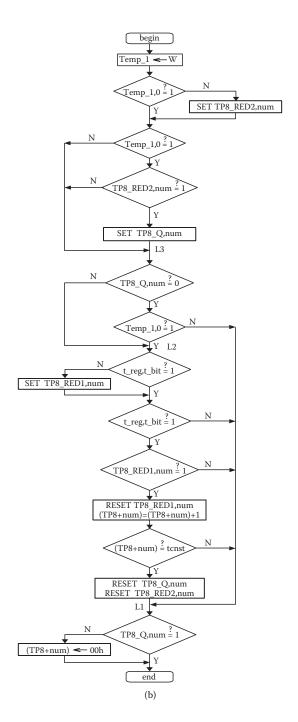

|   | 5.6   | Macro TP 8 (8-Bit Pulse Timer)                     | 108 |

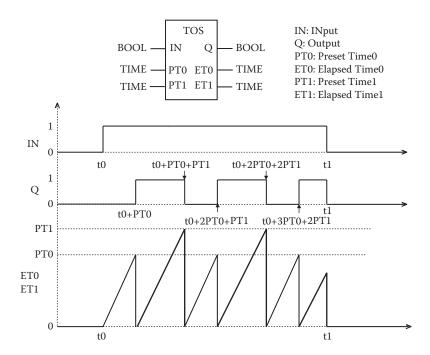

|   | 5.7   | Oscillator Timer (TOS)                             | 111 |

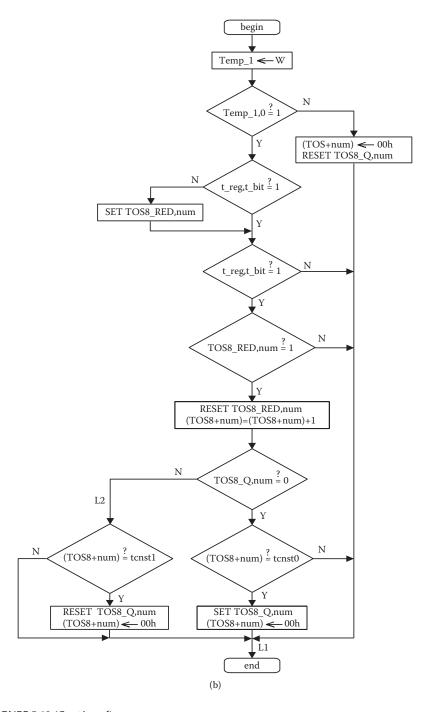

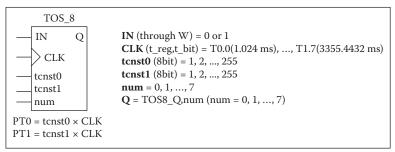

|   | 5.8   | Macro TOS 8 (8-Bit Oscillator Timer)               | 112 |

|   | 5.9   | Example for Timer Macros                           | 115 |

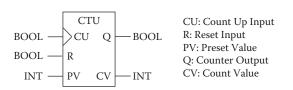

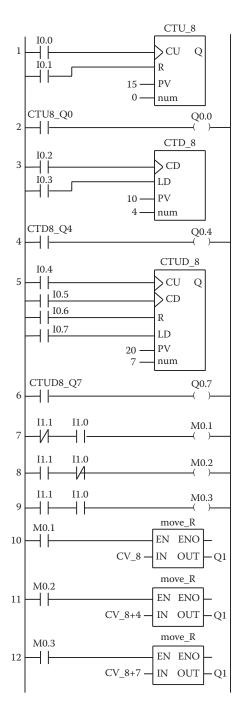

| 6 | Cou   | nter Macros                                        | 121 |

|   | 6.1   | Move and Load Macros                               |     |

|   | 6.2   | Counter Macros                                     |     |

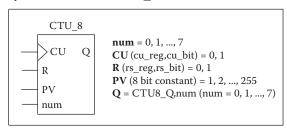

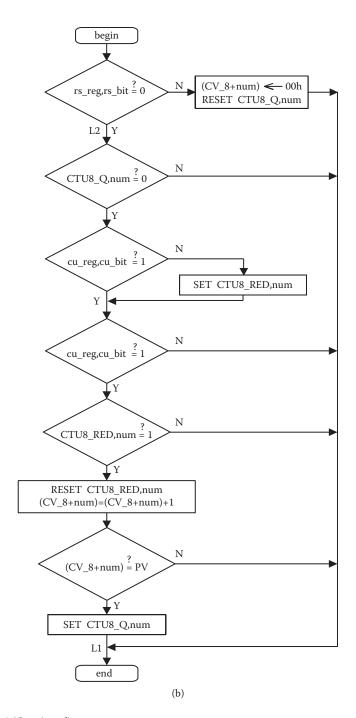

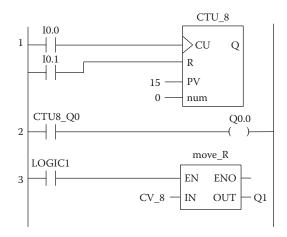

|   | 6.3   | Up Counter (CTU)                                   |     |

|   | 6.4   | Macro CTU 8 (8-Bit Up Counter)                     |     |

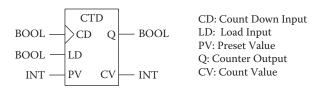

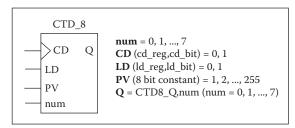

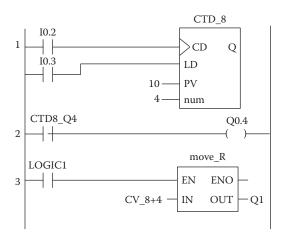

|   | 6.5   | Down Counter (CTD)                                 |     |

|   | 6.6   | Macro CTD 8 (8-Bit Down Counter)                   |     |

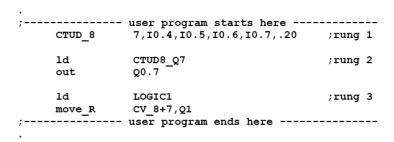

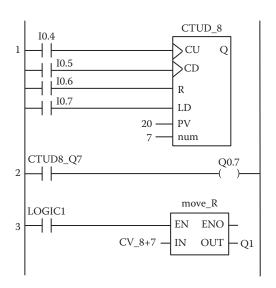

|   | 6.7   | Up/Down Counter (CTUD)                             |     |

|   | 6.8   | Macro CTUD 8 (8-Bit Up/Down Counter)               |     |

|   | 6.9   | Examples for Counter Macros                        |     |

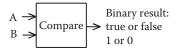

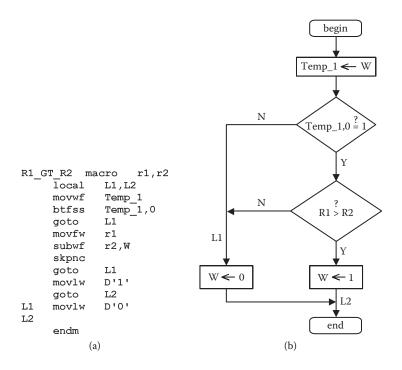

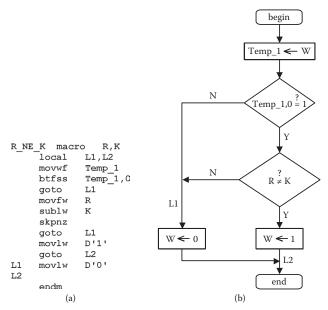

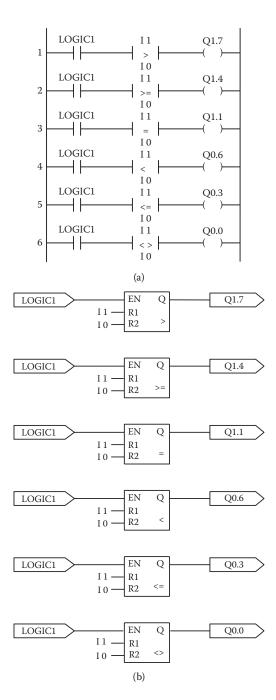

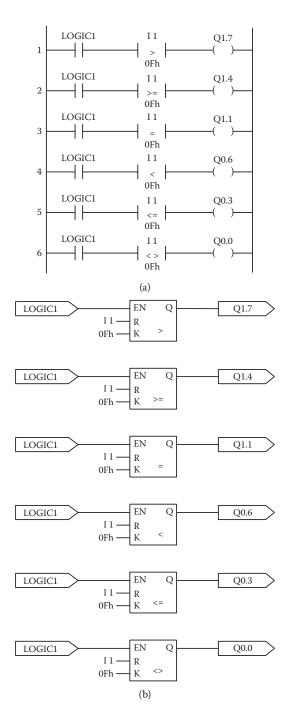

| 7 | Com   | parison Macros                                     | 143 |

|   | 7.1   | Macro R1 GT R2                                     |     |

|   | 7.2   | Macro R1 GE R2                                     |     |

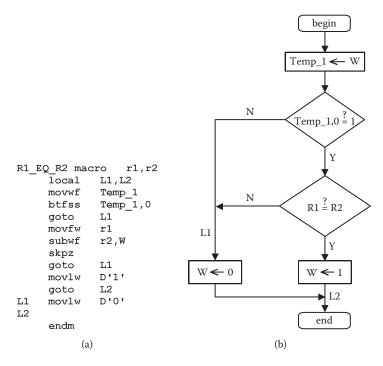

|   | 7.3   | Macro R1 EQ R2                                     |     |

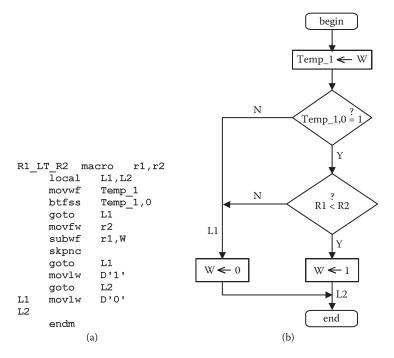

|   | 7.4   | Macro R1 LT R2                                     |     |

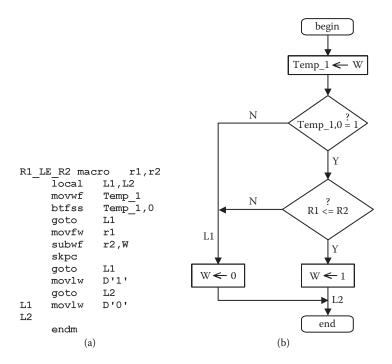

|   | 7.5   | Macro R1 LE R2                                     |     |

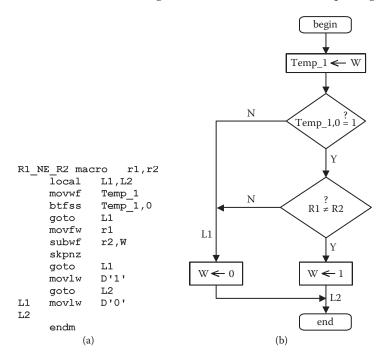

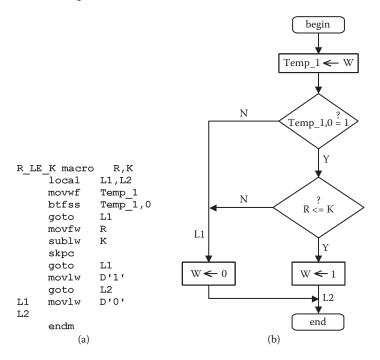

|    | 7.6   | Macro R1 NE R2                       | 150 |

|----|-------|--------------------------------------|-----|

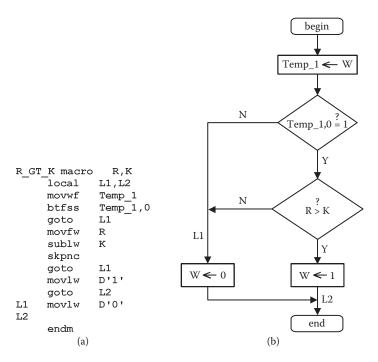

|    | 7.7   | Macro R GT K                         | 151 |

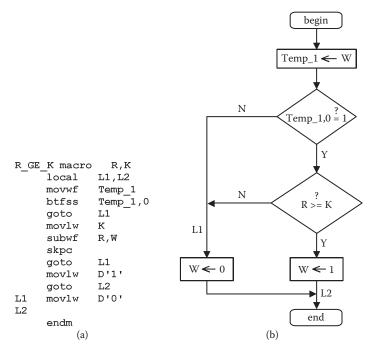

|    | 7.8   | Macro R GE K                         | 151 |

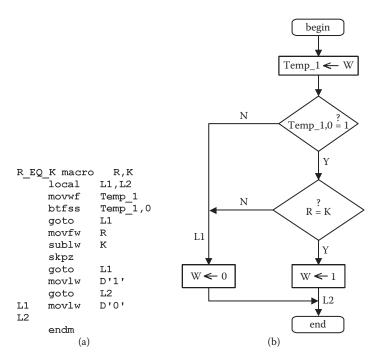

|    | 7.9   | Macro R EQ K                         |     |

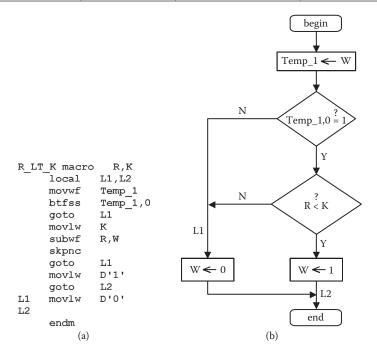

|    | 7.10  | Macro R LT K                         | 154 |

|    | 7.11  | Macro R LE K                         | 155 |

|    | 7.12  | Macro R NE K                         | 157 |

|    | 7.13  | Examples for Comparison Macros       | 158 |

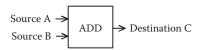

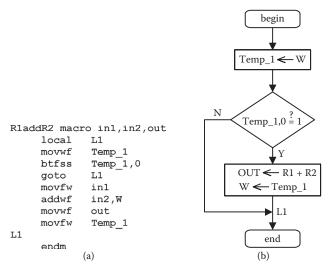

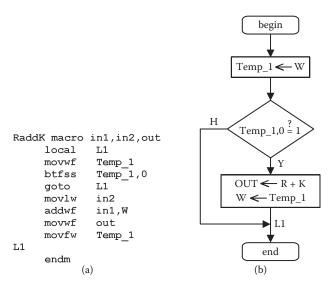

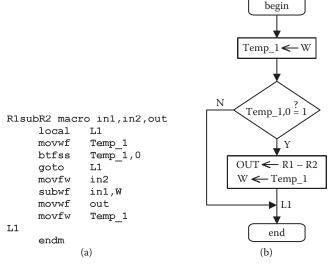

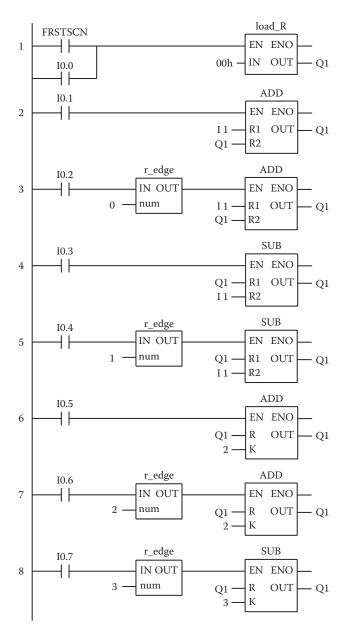

| 8  | Aritl | nmetical Macros                      | 163 |

|    | 8.1   | Macro R1addR2                        | 164 |

|    | 8.2   | Macro RaddK                          | 165 |

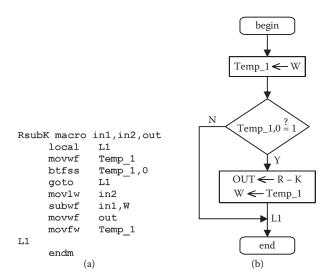

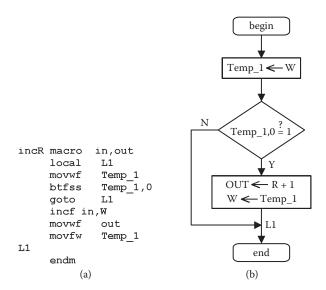

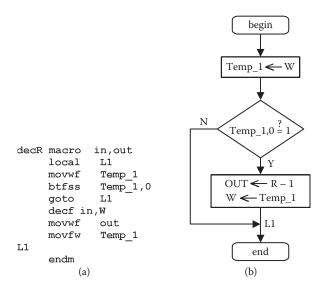

|    | 8.3   | Macro R1subR2                        | 165 |

|    | 8.4   | Macro RsubK                          | 167 |

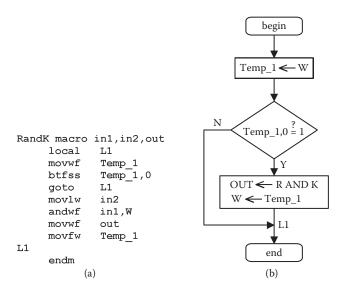

|    | 8.5   | Macro incR                           | 168 |

|    | 8.6   | Macro decR                           | 169 |

|    | 8.7   | Examples for Arithmetical Macros     | 170 |

| 9  | Logi  | cal Macros                           | 175 |

|    | 9.1   | Macro R1andR2                        |     |

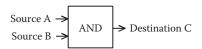

|    | 9.2   | Macro RandK                          | 177 |

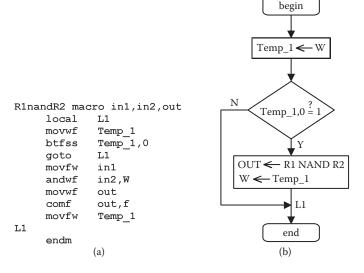

|    | 9.3   | Macro R1nandR2                       | 177 |

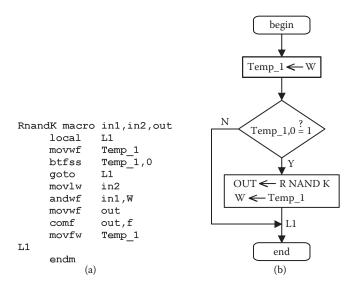

|    | 9.4   | Macro RnandK                         | 179 |

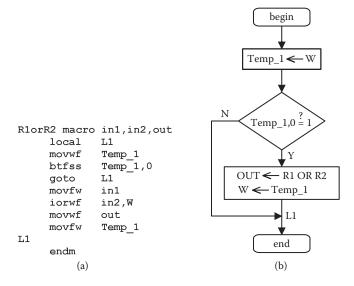

|    | 9.5   | Macro R1orR2                         | 180 |

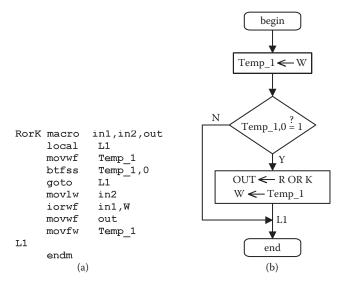

|    | 9.6   | Macro Rork                           | 181 |

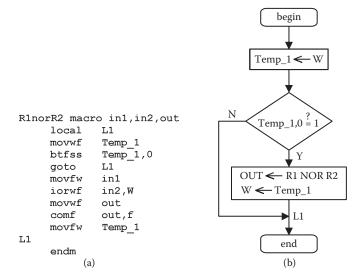

|    | 9.7   | Macro R1norR2                        | 182 |

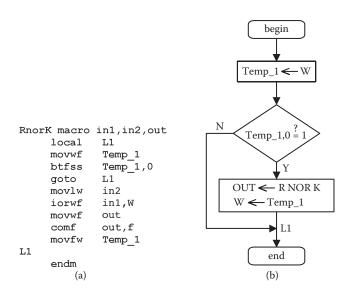

|    | 9.8   | Macro RnorK                          | 183 |

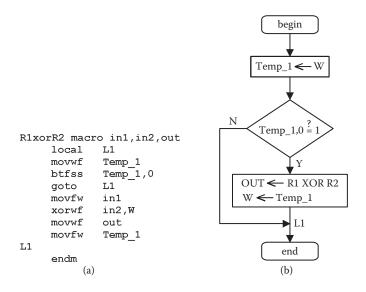

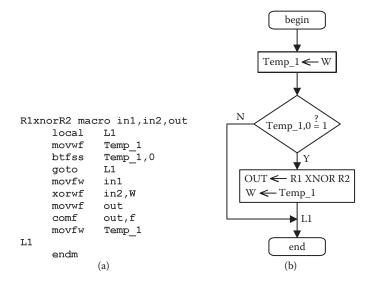

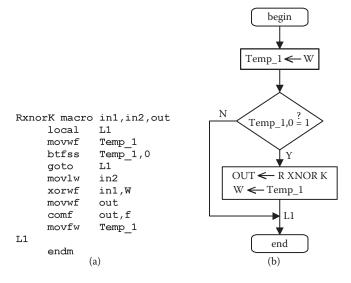

|    | 9.9   | Macro R1xorR2                        | 185 |

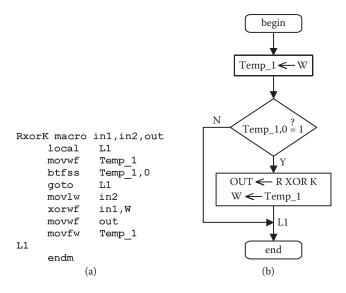

|    | 9.10  | Macro RxorK                          | 186 |

|    | 9.11  | Macro R1xnorR2                       | 187 |

|    | 9.12  | Macro RxnorK                         | 187 |

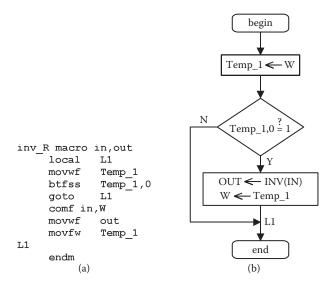

|    | 9.13  | Macro inv_R                          | 189 |

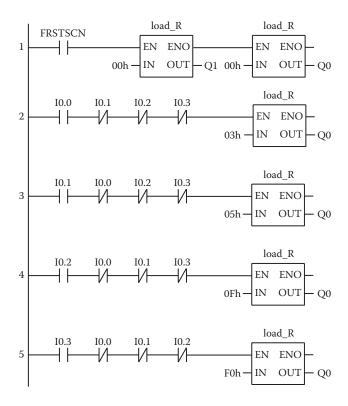

|    | 9.14  | Example for Logical Macros           | 190 |

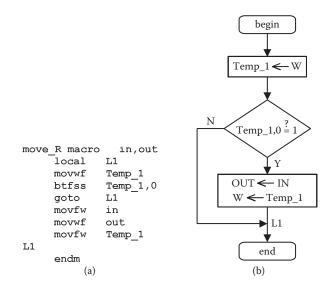

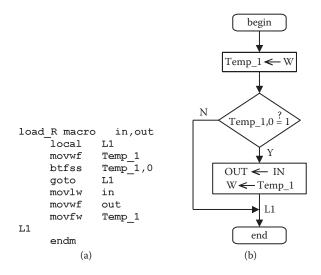

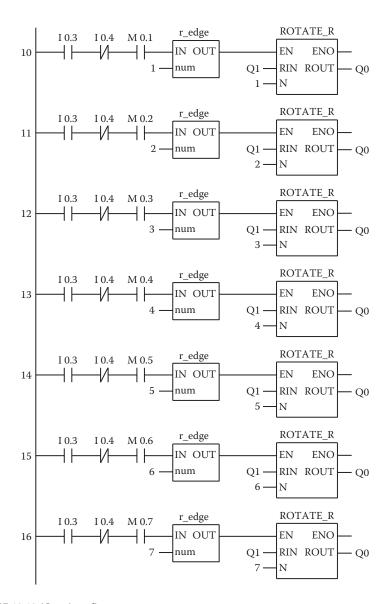

| 10 | Shift | t and Rotate Macros                  |     |

|    | 10.1  |                                      |     |

|    | 10.2  |                                      |     |

|    | 10.3  | Macro rotate_R                       |     |

|    | 10.4  | Macro rotate_L                       |     |

|    | 10.5  | Macro Swap                           | 209 |

|    | 10.6  | Examples for Shift and Rotate Macros | 210 |

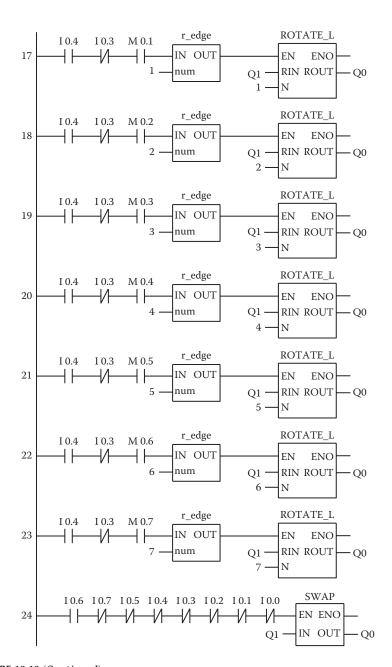

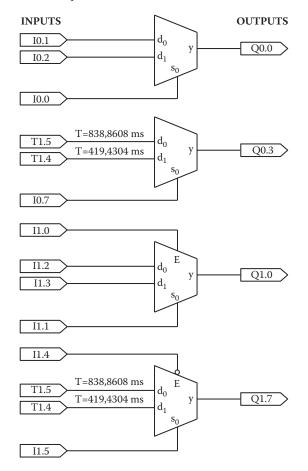

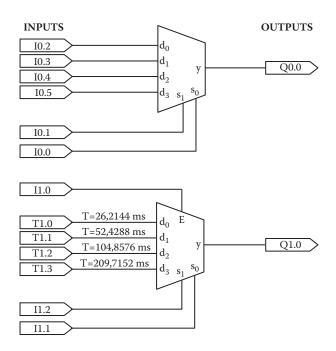

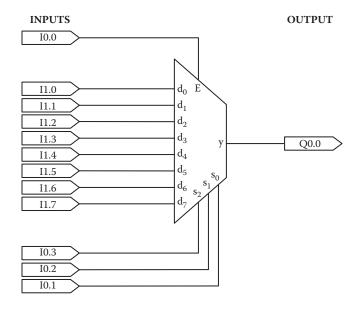

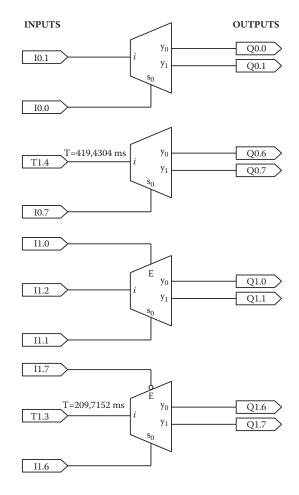

| 11 | Mult  | iiplexer Macros                      |     |

|    | 11.1  | Macro mux_2_1                        | 225 |

|    | 11.2  | Macro mux 2 1 E                      | 226 |

x Contents

|    | 11.3  | Macro mux 4 1                               | 227 |

|----|-------|---------------------------------------------|-----|

|    | 11.4  | Macro mux 4 1 E                             |     |

|    | 11.5  | Macro mux 8 1                               |     |

|    | 11.6  | Macro mux 8 1 E                             |     |

|    | 11.7  | Examples for Multiplexer Macros             |     |

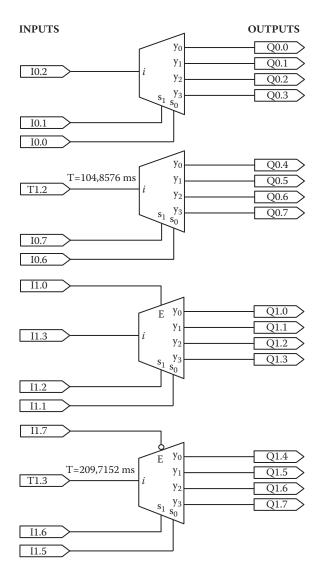

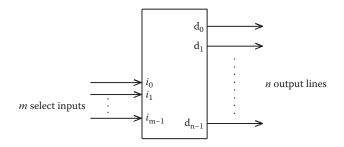

| 12 | Dem   | ultiplexer Macros                           | 243 |

|    | 12.1  | Macro Dmux 1 2                              |     |

|    | 12.2  | Macro Dmux 1 2 E                            |     |

|    | 12.3  | Macro Dmux 1 4                              |     |

|    | 12.4  | Macro Dmux_1_4_E                            |     |

|    | 12.5  | Macro Dmux 1 8                              |     |

|    | 12.6  | Macro Dmux 1 8 E                            |     |

|    | 12.7  | Examples for Demultiplexer Macros           |     |

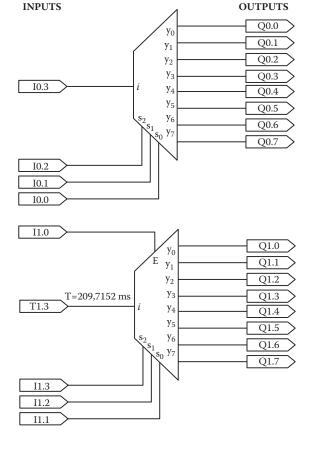

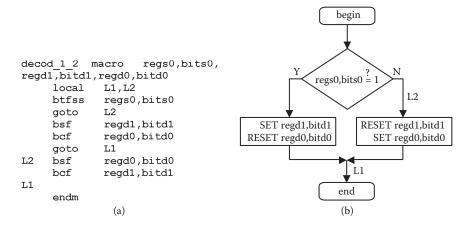

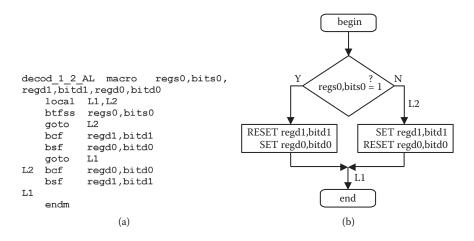

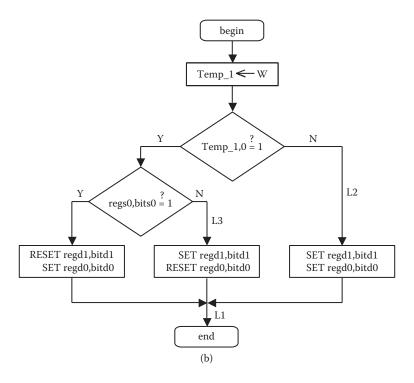

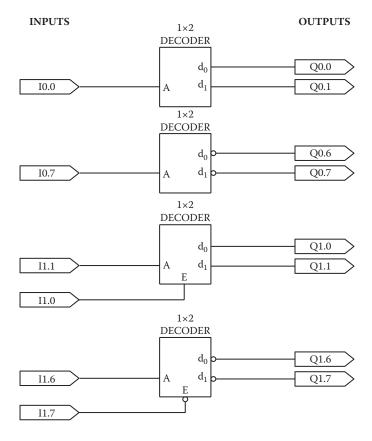

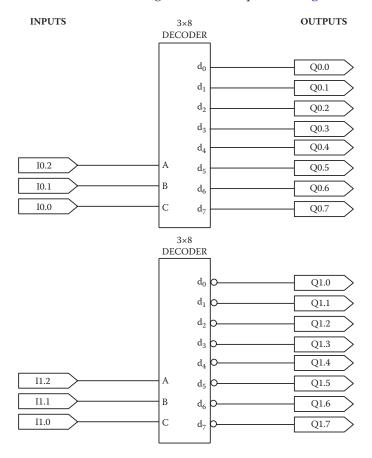

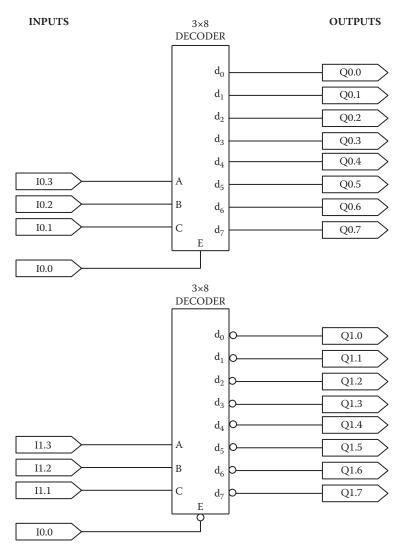

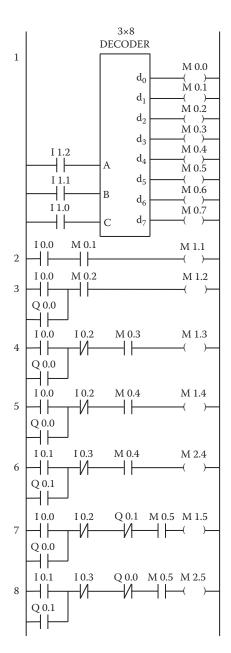

| 13 | Deco  | der Macros                                  | 263 |

|    | 13.1  | Macro decod 1 2                             | 264 |

|    | 13.2  | Macro decod 1 2 AL                          |     |

|    | 13.3  | Macro decod_1_2_E                           | 266 |

|    | 13.4  | Macro decod_1_2_E_AL                        |     |

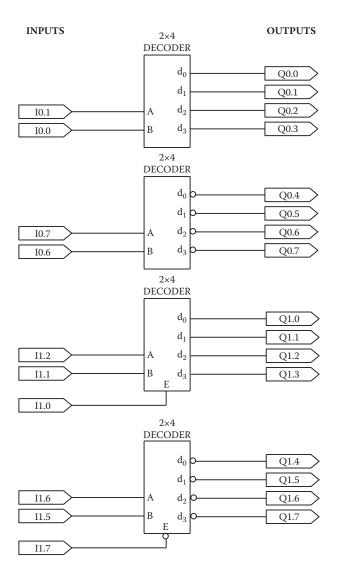

|    | 13.5  | Macro decod_2_4                             | 269 |

|    | 13.6  | Macro decod_2_4_AL                          | 270 |

|    | 13.7  | Macro decod_2_4_E                           | 273 |

|    | 13.8  | Macro decod_2_4_E_AL                        | 273 |

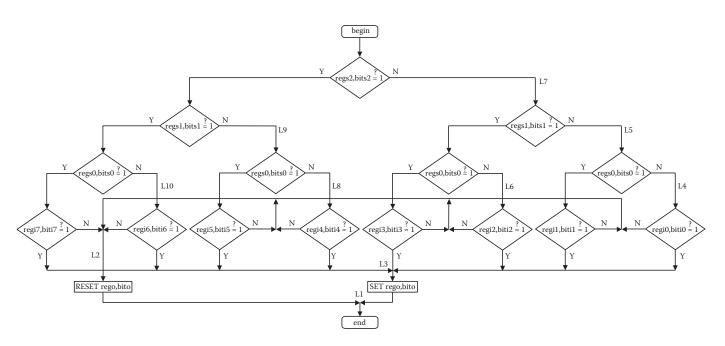

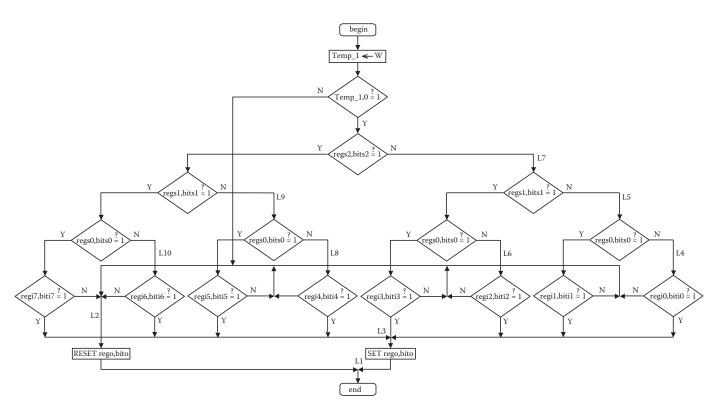

|    | 13.9  | Macro decod_3_8                             |     |

|    |       | Macro decod_3_8_AL                          |     |

|    |       | Macro decod_3_8_E                           |     |

|    |       | Macro decod_3_8_E_AL                        |     |

|    | 13.13 | Examples for Decoder Macros                 | 286 |

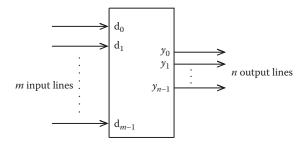

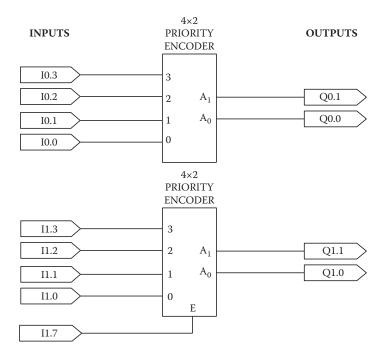

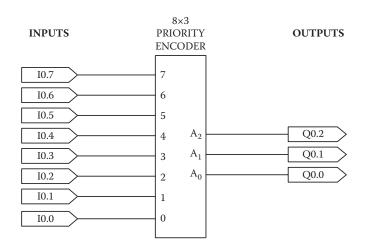

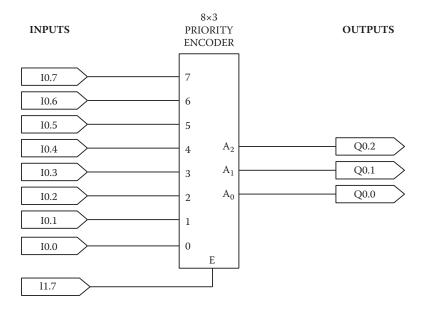

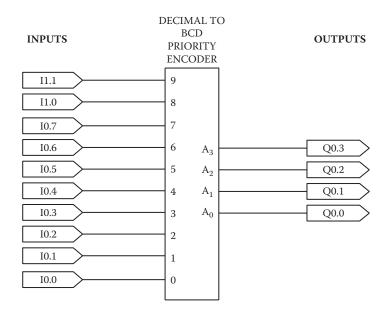

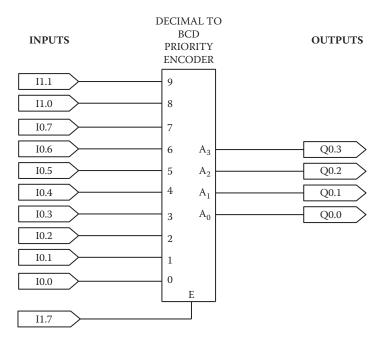

| 14 | Prior | ity Encoder Macros                          | 295 |

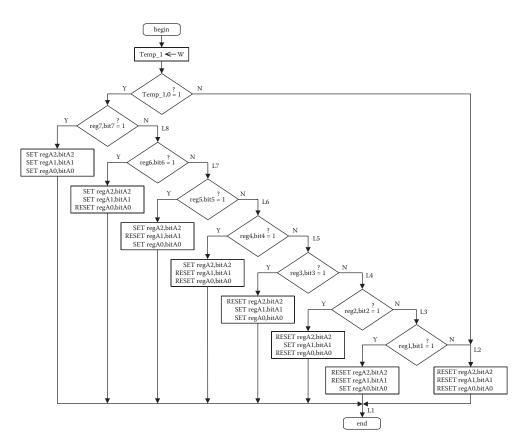

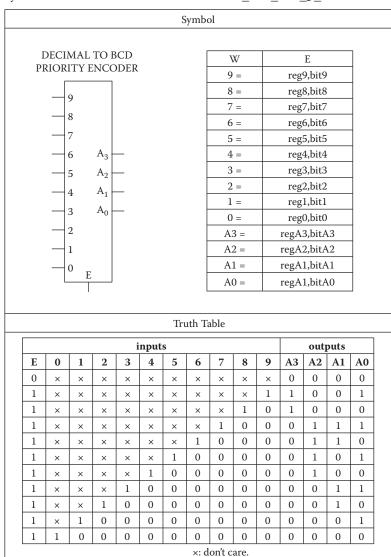

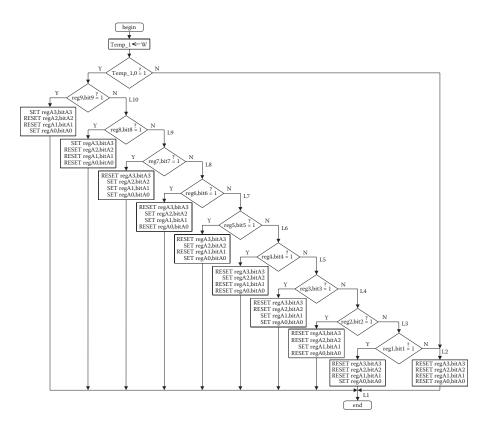

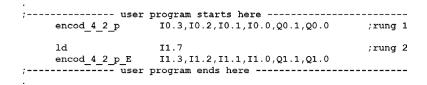

|    | 14.1  | Macro encod_4_2_p                           |     |

|    | 14.2  | Macro encod_4_2_p_E                         |     |

|    | 14.3  | Macro encod_8_3_p                           |     |

|    | 14.4  | Macro encod_8_3_p_E                         |     |

|    | 14.5  | Macro encod_dec_bcd_p                       |     |

|    | 14.6  | Macro encod_dec_bcd_p_E                     | 304 |

|    | 14.7  | Examples for Priority Encoder Macros        | 312 |

| 15 | Appl  | ication Example                             |     |

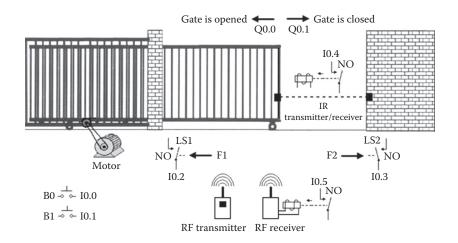

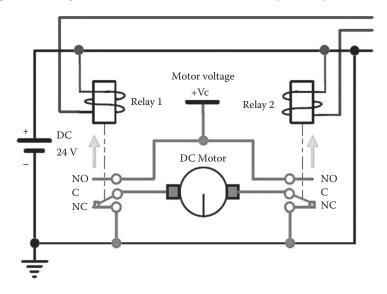

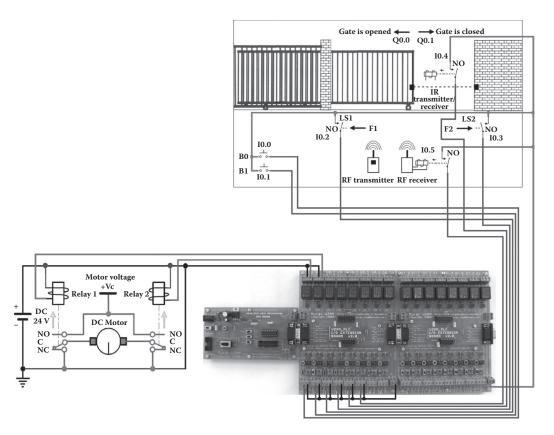

|    | 15.1  | Remotely Controlled Model Gate System       |     |

|    | 15.2  | Control Scenarios for the Model Gate System |     |

|    | 15.3  | Solutions for the Control Scenarios         |     |

|    |       | 15.3.1 Solution for the First Scenario      |     |

|    |       | 15.3.2 Solution for the Second Scenario     | 324 |

Contents xi

| 15.3.3         | Solution for the Third Scenario   | 325 |

|----------------|-----------------------------------|-----|

| 15.3.4         | Solution for the Fourth Scenario  | 326 |

| 15.3.5         | Solution for the Fifth Scenario   | 327 |

| 15.3.6         | Solution for the Sixth Scenario   | 328 |

| 15.3.7         | Solution for the Seventh Scenario | 329 |

| 15.3.8         | Solution for the Eighth Scenario  | 330 |

| About the CD-R | ROM                               | 337 |

| References     |                                   | 339 |

|                |                                   |     |

| Index          |                                   | 341 |

### Preface

Programmable logic controllers (PLCs) have been used extensively in industry for the past five decades. PLC manufacturers offer different PLCs in terms of functions, program memories, and the number of inputs/outputs (I/Os), ranging from a few to thousands of I/Os. The design and implementation of PLCs have long been a secret of the PLC manufacturers. Recently, a serious work was reported by the author of this book to describe a microcontroller-based implementation of a PLC. With a series of 22 articles published in *Electronics World* magazine (http://www.electronicsworld.co.uk/) between the years 2008 and 2010, the design and implementation of a PIC16F648A-based PLC were described. This book is based on an improved version of the project reported in *Electronics World* magazine.

This book is written for advanced students, practicing engineers, and hobbyists who want to learn how to design and use a microcontroller-based PLC. The book assumes the reader has taken courses in digital logic design, microcontrollers, and PLCs. In addition, the reader is expected to be familiar with the PIC16F series of microcontrollers and to have been exposed to writing programs using PIC assembly language within an MPLAB integrated development environment.

The CD-ROM that accompanies this book contains all the program source files and hex files for the examples described in the book. In addition, PCB files of the CPU and I/O extension boards of the PIC16F648A-based PLC are also included on the CD-ROM.

Dr. Murat Uzam

Melikşah Üniversitesi Mühendislik-Mimarlık Fakültesi Elektrik-Elektronik Mühendisliği Bölümü Talas, Kayseri Turkey

### Acknowledgments

I am grateful to Dr. Gökhan Gelen (gokhan\_gelen@hotmail.com) for his great effort in drawing the printed circuit boards (PCBs) and for producing the prototypes of the CPU board and the I/O extension board. Without his help this project may have been delayed for years.

### Background and Use of the Book

This project was completed during the search for an answer to the following question: How could one design and implement a programmable logic controller (PLC)? The answer to this question was partially discovered about 15 years ago by the author in a freely available PLC project called PICBIT. The file, called picbit.inc of PICBIT, contains the basic PLC macro definitions. The PIC16F648A-based PLC project has been completed by the inspiration of these macros. Of course many new features have been included within the PIC16F648A-based PLC project to make it an almost perfect PLC. The reader should be aware that this project does not include graphical interface PC software as in PICBIT or in other PLCs for developing PLC programs. Rather, PLC programs are developed by using macros as done in the Instruction List (IL) PLC programming language. An interested and skilled reader could well (and is encouraged to) develop graphical interface PC software for easy use of the PIC16F648A-based PLC.

The PIC16F648A-based PLC project was first reported in a series of 22 articles published in *Electronics World* magazine (http://www.electronicsworld.co.uk/) between the years 2008 and 2010 [1–22]. All details of this project can be viewed at http://www.meliksah.edu.tr/muzam/UZAM\_PLC\_with\_PIC16F648A.htm [23]. This book is based on an improved version of the project reported in *Electronics World* magazine. The improvements are summarized as follows:

- 1. The current hardware has two boards: the CPU board and the I/O extension board. In the previous version of the hardware, the main board consisted of the CPU board and eight inputs/eight outputs, while in the current version, the CPU board excludes eight inputs/eight outputs. Thus, the CPU board is smaller than the previous main board. In addition, the current I/O extension board is also smaller than in the previous version.

- 2. The hardware explained in this book consists of one CPU board and two I/O extension boards. Therefore, the current version of the software supports 16 inputs and 16 outputs, while the previous one supported 8 inputs and 8 outputs.

- 3. Clock frequency was 4 MHz in the previous version, but is 20 MHz in the current version.

- 4. Some of the macros are improved compared with the previous versions.

- 5. Flowcharts are provided to help the understanding of all macros (functions).

In order to properly follow the topics explained in this book, it is expected that the reader will construct his or her PIC16F648A-based PLC consisting of the CPU board and two I/O extension boards using the PCB files provided within the CD-ROM attached to this book. In this book, as the PIC assembly is used as the programming language within the MPLAB integrated development environment (IDE), the reader is referred to the homepage of Microchip (http://www.microchip.com/) to obtain the latest version of MPLAB IDE. References [24] and [25] may be useful to understand some aspects of the PIC16F648A microcontroller and MPASM™ assembler, respectively.

The contents of the book's 15 chapters are explained briefly, as follows:

- 1. **Hardware:** In this chapter, the hardware structure of the PIC16F648A-based PLC, consisting of 16 discrete inputs and 16 discrete outputs, is explained in detail.

- 2. **Basic software:** This chapter explains the basic software structure of the PIC16F648A-based PLC. A PLC scan cycle includes the following: obtain the inputs, run the user program, and update the outputs. In addition, it is also necessary to define and initialize all variables used within a PLC. Necessary functions are all described as PIC assembly macros to be used in the PIC16F648A-based PLC. The macros described in this chapter can be summarized as follows: HC165 (for handling the inputs), HC595 (for sending the outputs), dbncr0 and dbncr1 (for debouncing 16 inputs), initialize, get\_inputs, and send\_outputs.

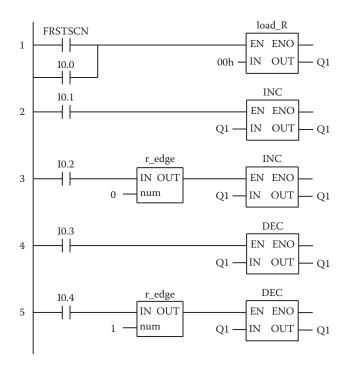

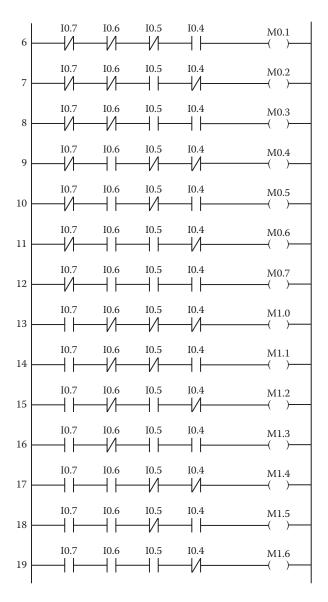

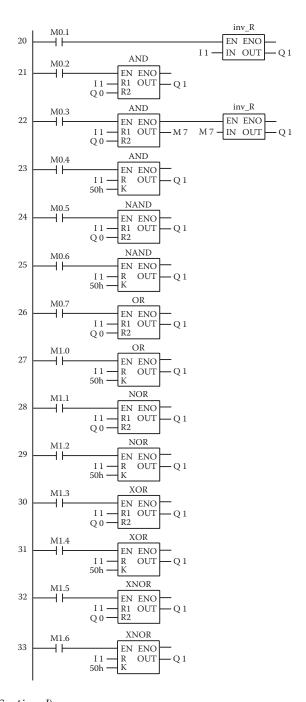

- 3. Contact and relay-based macros: The following contact and relay-based macros are described in this chapter: ld (load), ld\_not (load\_not), not, or, or\_not, nor, and, and\_not, nand, xor, xor\_not, xnor, out, out\_not, in\_out, inv\_out, \_set, \_reset. These macros are defined to operate on 1-bit (Boolean) variables.

- 4. Flip-flop macros: The following flip-flop-based macros are described in this chapter: r\_edge (rising edge), f\_edge (falling edge), latch0, latch1, dff\_r (rising edge triggered D flip-flop), dff\_f (falling edge triggered D flip-flop), tff\_r (rising edge triggered T flip-flop), tff\_f (falling edge triggered T flip-flop), jkff\_r (rising edge triggered JK flip-flop), and jkff\_f (falling edge triggered JK flip-flop).

- 5. **Timer macros:** The following timer macros are described in this chapter: TON\_8 (8-bit on-delay timer), TOF\_8 (8-bit off-delay timer), TP 8 (8-bit pulse timer), and TOS 8 (8-bit oscillator timer).

- 6. **Counter macros:** The following counter macros are described in this chapter: CTU\_8 (8-bit up counter), CTD\_8 (8-bit down counter), and CTUD 8 (8-bit up/down counter).

- 7. **Comparison macros:** The comparison macros are described in this chapter. The contents of two registers (R1 and R2) are compared according to the following: GT (greater than, >), GE (greater than or equal to, ≥), EQ (equal to, =), LT (less than, <), LE (less than or equal to, ≤), and NE (not equal to, ≠). Similar comparison macros are also described for comparing the contents of an 8-bit register (R) with an 8-bit constant (K).

- 8. **Arithmetical macros:** The arithmetical macros are described in this chapter. The following operators are applied to the contents of two registers (R1 and R2): ADD, SUB (subtract), INC (increment), and DEC (decrement). Similar arithmetical macros are also described, to be used with the contents of an 8-bit register (R) and an 8-bit constant (K).

- 9. **Logical macros:** The following logical macros are described in this chapter: inv\_R, AND, NAND, OR, NOR, XOR, and XNOR. These macros are applied to an 8-bit register (R1) with another register (R2) or an 8-bit constant (K).

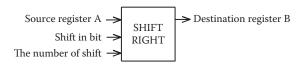

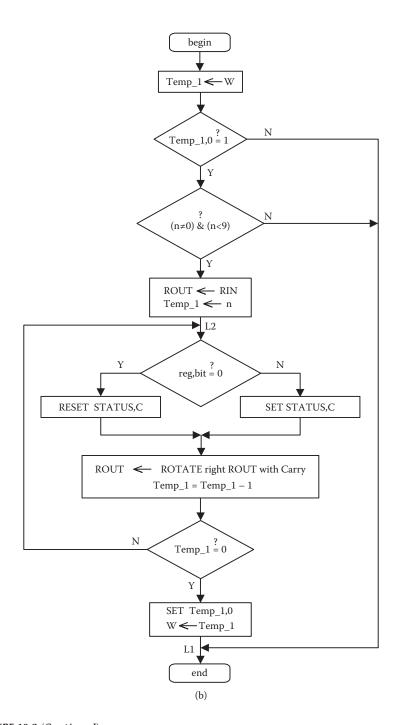

- 10. **Shift and rotate macros:** The following shift and rotate macros are described in this chapter: SHIFT\_R (shift right the content of register R), SHIFT\_L (shift left the content of register R), ROTATE\_R (rotate right the content of register R), ROTATE\_L (rotate left the content of register R), and SWAP (swap the nibbles of a register).

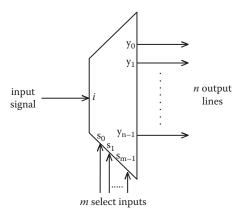

- 11. **Multiplexer macros:** The following multiplexer macros are described in this chapter: mux\_2\_1 (2×1 MUX), mux\_2\_1\_E (2×1 MUX with enable input), mux\_4\_1 (4×1 MUX), mux\_4\_1\_E (4×1 MUX with enable input), mux\_8\_1 (8×1 MUX), and mux\_8\_1\_E (8×1 MUX with enable input).

- 12. **Demultiplexer macros:** The following demultiplexer macros are described in this chapter: Dmux\_1\_2 (1×2 DMUX), Dmux\_1\_2\_E (1×2 DMUX with enable input), Dmux\_1\_4 (1×4 DMUX), Dmux\_1\_4\_E (1×4 DMUX with enable input), Dmux\_1\_8 (1×8 DMUX), and Dmux\_1\_8\_E (1×8 DMUX with enable input).

- 13. **Decoder macros:** The following decoder macros are described in this chapter: decod\_1\_2 (1×2 decoder), decod\_1\_2\_AL (1×2 decoder with active low outputs), decod\_1\_2\_E (1×2 decoder with enable input), decod\_1\_2\_E\_AL (1×2 decoder with enable input and active low outputs), decod\_2\_4 (2×4 decoder), decod\_2\_4\_AL (2×4 decoder with active low outputs), decod\_2\_4\_E\_AL (2×4 decoder with enable input), decod\_2\_4\_E\_AL (2×4 decoder with enable input and active low outputs), decod\_3\_8\_AL (3×8 decoder with enable input), and

- decod\_3\_8\_E\_AL (3×8 decoder with enable input and active low outputs).

- 14. **Priority encoder macros:** The following priority encoder macros are described in this chapter: encod\_4\_2\_p (4×2 priority encoder), encod\_4\_2\_p\_E (4×2 priority encoder with enable input), encod\_8\_3\_p (8×3 priority encoder), encod\_8\_3\_p\_E (8×3 priority encoder with enable input), encod\_dec\_bcd\_p (decimal to binary coded decimal [BCD] priority encoder), and encod\_dec\_bcd\_p\_E (decimal to BCD priority encoder with enable input).

- 15. **Application example:** This chapter describes an example remotely controlled model gate system and makes use of the PIC16F648A-based PLC to control it for different control scenarios.

Table 1 shows the general characteristics of the PIC16F648A-based PLC.

**TABLE 1**General Characteristics of the PIC16F648A-Based PLC

| Inputs/Outputs/Functions                              | Byte Addresses/<br>Related Bytes | Bit Addresses or Function<br>Numbers                                             |

|-------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|

| 16 discrete inputs<br>(external inputs: 5 or 24 V DC) | I0<br>I1                         | I0.0, I0.1,, I0.7<br>I1.0, I1.1,, I1.7                                           |

| 16 discrete outputs (relay type outputs)              | Q0<br>Q1                         | Q0.0, Q0.1,, Q0.7<br>Q1.0, Q1.1,, Q1.7                                           |

| 32 internal relays<br>(memory bits)                   | M0<br>M1<br>M2<br>M3             | M0.0, M0.1,, M0.7<br>M1.0, M1.1,, M1.7<br>M2.0, M2.1,, M2.7<br>M3.0, M3.1,, M3.7 |

| 8 rising edge detectors                               | RED                              | r_edge (0, 1,, 7)                                                                |

| 8 falling edge detectors                              | FED                              | f_edge (0, 1,, 7)                                                                |

| 8 rising edge triggered<br>D flip-flop                | DFF_RED                          | dff_r (0, 1,, 7), regi,biti, rego,bito                                           |

| 8 falling edge triggered<br>D flip-flop               | DFF_FED                          | dff_f (0, 1,, 7), regi,biti, rego,bito                                           |

| 8 rising edge triggered<br>T flip-flop                | TFF_RED                          | tff_r (0, 1,, 7), regi,biti, rego,bito                                           |

| 8 falling edge triggered<br>T flip-flop               | TFF_FED                          | tff_f (0, 1,, 7), regi,biti, rego,bito                                           |

| 8 rising edge triggered<br>JK flip-flop               | JKFF_RED                         | jkff_r (0, 1,, 7), regi,biti,<br>rego,bito                                       |

| 8 falling edge triggered<br>JK flip-flop              | JKFF_FED                         | jkff_f (0, 1,, 7), regi,biti,<br>rego,bito                                       |

**TABLE 1 (CONTINUED)**General Characteristics of the PIC16F648A-Based PLC

| Inputs/Outputs/Functions                 | Byte Addresses/<br>Related Bytes                     | Bit Addresses or Function<br>Numbers    |

|------------------------------------------|------------------------------------------------------|-----------------------------------------|

| 8 on-delay timers                        | TON8, TON8+1,,<br>TON8+7<br>TON8_Q<br>TON8_RED       | TON8_Q0<br>TON8_Q1,<br>TON8_Q7          |

| 8 off-delay timers                       | TOF8, TOF8+1,,<br>TOF8+7, TOF8_Q<br>TOF8_RED         | TOF8_Q0<br>TOF8_Q1,<br>TOF8_Q7          |

| 8 pulse timers                           | TP8, TP8+1,, TP8+7,<br>TP8_Q<br>TP8_RED1<br>TP8_RED2 | TP8_Q0<br>TP8_Q1,<br>TP8_Q7             |

| 8 oscillator timers                      | TOS8, TOS8+1,,<br>TOS8+7<br>TOS8_Q<br>TOS8_RED       | TOS8_Q0<br>TOS8_Q1,<br>TOS8_Q7          |

| 8 counters                               | CV8,<br>CV8+1,, CV8+7                                | CTU8_Q0<br>CTU8_Q1,<br>CTU8_Q7          |

| CTU: up counter                          | CTU8_Q<br>CTU8_RED<br>CTD8_Q<br>CTD8_RED             | or<br>CTD8_Q0<br>CTD8_Q1,<br>CTD8_Q7    |

| CTD: down counter  CTUD: up/down counter | CTUD8_Q<br>CTUD8_RED                                 | or<br>CTUD8_Q0<br>CTUD8_Q1,<br>CTUD8_Q7 |

*Note*: regi, biti, input bit; rego, bito, output bit.

At any time, a total of eight different counters can be used.

### About the Author

Murat Uzam was borned in Söke, Turkey, in 1968. He received his BSc and MSc degrees from the Electrical Engineering Department of Yıldız Technical University, İstanbul, Turkey, in 1989 and 1991, respectively. He received his PhD degree from the University of Salford, Salford, UK, in 1998. He is currently a professor in the Department of Electrical and Electronics Engineering at Melikşah University in Kayseri, Turkey.

Dr. Uzam's research interests include the design and implementation of discrete event control systems modeled by Petri nets (PN) and, in particular, deadlock prevention/liveness enforcement in flexible manufacturing systems, Programmable

Logic Controllers (PLCs), microcontrollers (especially PIC microcontrollers), and the design of microcontroller-based PLCs. The details of his studies are accessible from his web page: http://www.meliksah.edu.tr/muzam.

### Hardware of the PIC16F648A-Based PLC

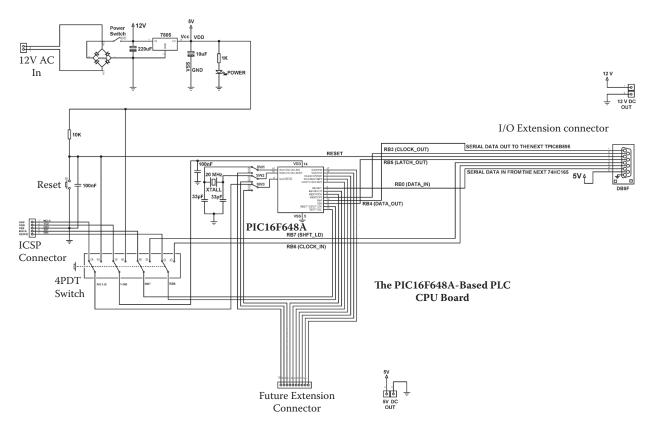

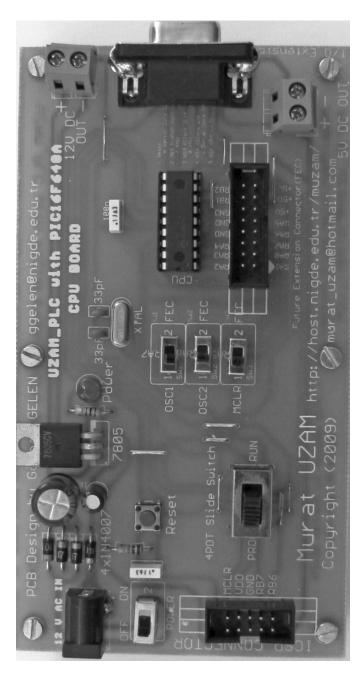

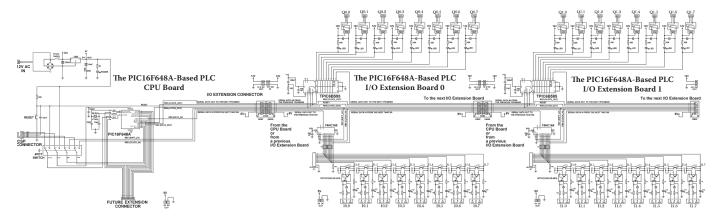

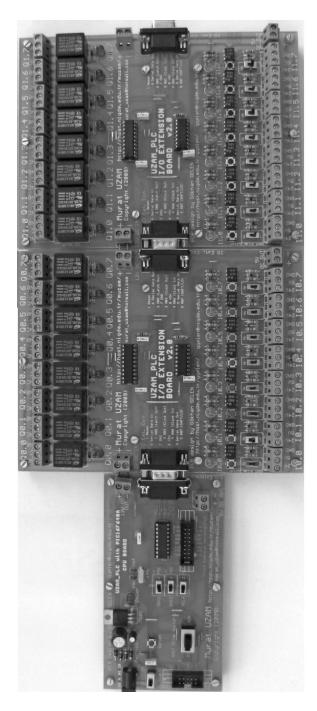

The hardware of the PIC16F648A-based programmable logic controller (PLC) consists of two parts: the *CPU board* and the *I/O extension board*. The schematic diagram and the photograph of the PIC16F648A-based PLC CPU board are shown in Figures 1.1 and 1.2, respectively. The CPU board contains mainly three sections: power, programming, and CPU (central processor unit).

The power section accepts 12 V AC input and produces two DC outputs: 12 VDC, to be used as the operating voltage of relays, and 5 VDC, to be used for ICs, inputs, etc. The programming section deals with the programming of the PIC16F648A microcontroller. For programming the PIC16F648A in circuit, it is necessary to use PIC programmer hardware and software with In Circuit Serial Programming (ICSP) capability. For related hardware and software to be used for programming the PIC16F648A-based PLC, please visit the following web page: http://www.meliksah.edu.tr/muzam/. For other types of USB, serial, or parallel port PIC programmers the reader is expected to make necessary arrangements. The ICSP connector takes the lines VPP(MCLR), VDD, VSS(GND), DATA (RB7), and CLOCK (RB6) from the PIC programmer hardware through a properly prepared cable, and it connects them to a four-pole double-throw (4PDT) switch. There are two positions of the 4PDT switch. As seen from Figure 1.1, in one position of the 4PDT switch, PIC16F648A is ready to be programmed, and in the other position the loaded program is run. For properly programming the PIC16F648A by means of a PIC programmer and the 4PDT switch, it is also a necessity to switch off the power switch. The CPU section consists of the PIC16F648A microcontroller. In the project reported in this book, the PLC is fixed to run at 20 MHz with an external oscillator. This frequency is fixed because time delays are calculated based on this speed. By means of two switches, SW1 and SW2, it is also possible to use another internal or external oscillator with different crystal frequencies. When doing so, time delay functions must be calculated accordingly. SW3 connects the RA5 pin either to one pole of the 4PDT switch or to the future extension connector. When programming PIC16F648A, RA5 should be connected to the 4PDT switch. RB0, RB6, and RB7 pins are all reserved to be used for 8-bit parallel-to-serial converter register 74HC/LS165. Through these three pins and with added 74HC/LS165 registers, we can describe as many inputs as necessary. RB0, RB6, and RB7 are the data in, clock in, and shift/load pins, respectively. Similarly, RB3, RB4, and RB5 pins are all reserved to be used for 8-bit serial-to-parallel converter register/driver TPIC6B595. Through these three pins and with added TPIC6B595 registers,

**FIGURE 1.1** Schematic diagram of the CPU board.

**FIGURE 1.2** Photograph of the CPU board.

we can describe as many outputs as necessary. RB3, RB4, and RB5 are the clock out, data out, and latch out pins, respectively. The remaining unused pins of the PIC16F648A are connected to the future extension connector. PIC16F648A provides the following: flash program memory (words), 4096; RAM data memory (bytes), 256; and EEPROM data memory (bytes), 256. The PIC16F648A-based PLC macros make use of registers defined in RAM data memory. Note that it may be possible to use PIC16F628A as the CPU, but one has to bear in mind that PIC16F628A provides the following: flash program memory (words), 2048; RAM data memory (bytes), 224; and EEPROM data memory (bytes), 128. In that case, it is necessary to take care of the usage of RAM data memory.

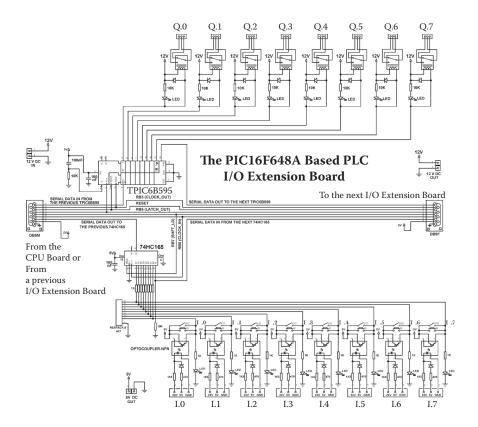

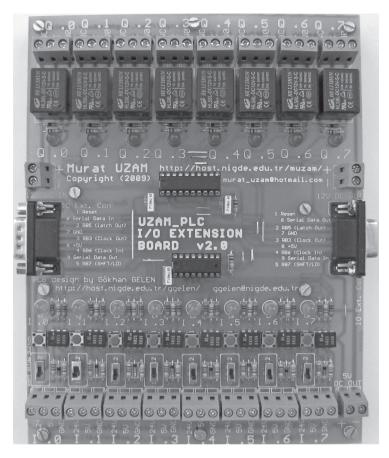

Figures 1.3 and 1.4 show the schematic diagram and photograph of the I/O extension board, respectively. The I/O extension board contains mainly two sections: eight discrete inputs and eight discrete outputs. The I/O extension connector DB9M seen on the left connects the I/O extension board to the CPU board or to a previous I/O extension board. Similarly, the I/O extension

**FIGURE 1.3** Schematic diagram of the I/O extension board.

**FIGURE 1.4** Photograph of the I/O extension board.

connector DB9F seen on the right connects the I/O extension board to a next I/O extension board. In this way we can connect as many I/O extension boards as necessary. Five-volt DC and 12 V DC are taken from the CPU board or from a previous I/O extension board, and they are passed to the next I/O extension boards. All I/O data are sent to and taken from all the connected extension I/O boards by means of I/O extension connectors DB9M and DB9F.

The *inputs section* introduces eight discrete inputs for the PIC16F648A-based PLC (called I0.0, I0.1, ..., I0.7 for the first I/O extension board). Five-volt DC or 24 V DC input signals can be accepted by each input. These external input signals are isolated from the other parts of the hardware by using NPN type opto-couplers (e.g., 4N25). For simulating input signals, one can use onboard push buttons as temporary inputs and slide switches as permanent inputs. In the beginning of each PLC scan cycle (get\_inputs) the 74HC/LS165 is loaded (RB7 (shift/load) = 0) with the level of eight inputs and then these

**FIGURE 1.5** Schematic diagram of the CPU board plus two I/O extension boards.

**FIGURE 1.6** Photograph of the CPU board plus two I/O extension boards.

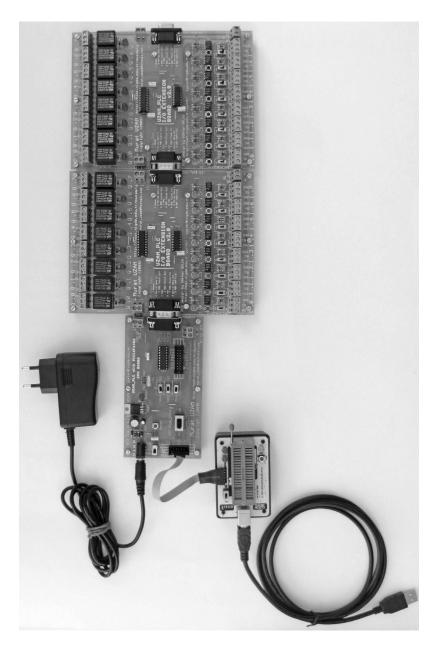

**FIGURE 1.7** Photograph of the CPU board plus two I/O extension boards and a USB PIC programmer.

data are serially clocked in (when RB7 = 1; through RB0 data in and RB6 clock in pins). If there is only one I/O extension board used, then eight clock\_in signals are enough to get the eight input signals. For each additional I/O extension board, eight more clock\_in signals are necessary. The serial data coming from the I/O extension board(s) are taken from the SI input of the 74HC/LS165.

The *outputs section* introduces eight discrete relay outputs for the PIC16F648A-based PLC (called Q0.0, Q0.1, ..., Q0.7 for the first I/O extension board). Each relay operates with 12 V DC and is driven by an 8-bit serial-to-parallel converter register/driver TPIC6B595. Relays have single-pole double-throw (SPDT) contacts with C (common), NC (normally closed), and NO (normally open) terminals. At the end of each PLC scan cycle (send\_outputs) the output data are serially clocked out (through RB3 clock out and RB4 data out pins) and finally latched within the TPIC6B595. If there is only one I/O extension board used, then eight clock\_out signals are enough to send the eight output signals. For each additional I/O extension board, eight more clock\_out signals are necessary. The serial data going to the I/O extension board(s) are sent out from the SER OUT (pin 18) of the TPIC6B595.

The PCB design files of both the CPU board and the I/O extension board can be obtained from the CD-ROM attached to this book. Note that in the PCB design of the CPU board and the I/O extension board, some lines of I/O extension connectors DB9M and DB9F are different from the ones shown in Figures 1.1 and 1.3.

The project reported in this book makes use of a CPU board and two I/O extension boards, as can be seen from the schematic diagram and photograph depicted in Figures 1.5 and 1.6, respectively. Thus, in total there are 16 inputs and 16 outputs. Figure 1.7 shows the PIC16F648A-based PLC consisting of a CPU board, I/O extension boards, 12 V DC adapter, and USB PIC programmer.

### Basic Software

In this chapter, the basic software of the PIC16F648A-based PLC is explained. A PLC scan cycle includes the following: obtain the inputs, run the user program, and update the outputs. It is also necessary to define and initialize all variables used within a PLC. Necessary functions are all described as PIC assembly macros to be used in the PIC16F648A-based PLC. The macros described in this chapter could be summarized as follows: HC165 (for handling the inputs), HC595 (for sending the outputs), dbncr0 and dbncr1 (for debouncing the inputs), initialize, get\_inputs, and send\_outputs. In addition, the concept of *contact bouncing* and how it is solved in the PIC16F648A-based PLC is explained in detail.

### 2.1 Basic Software Structure

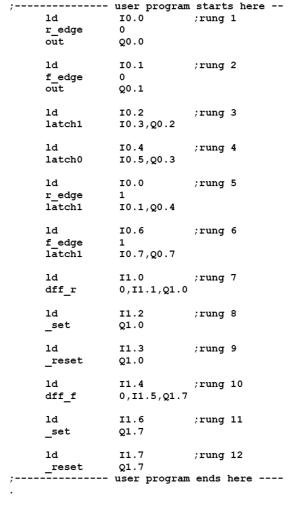

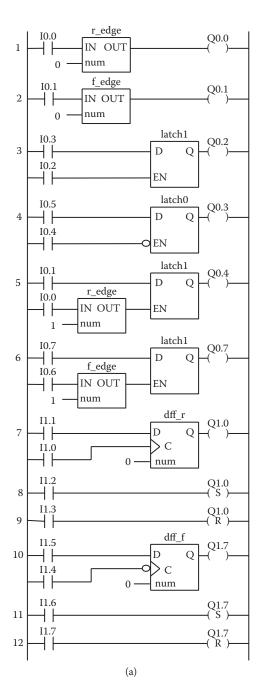

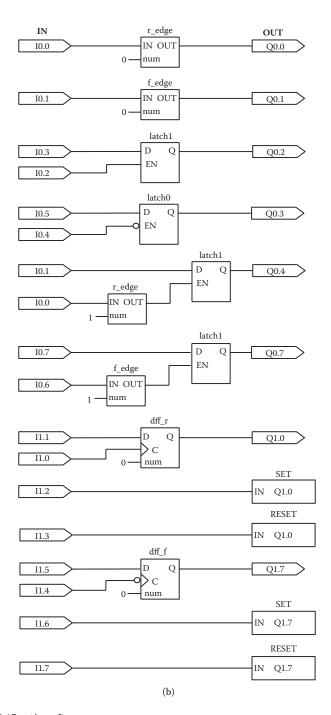

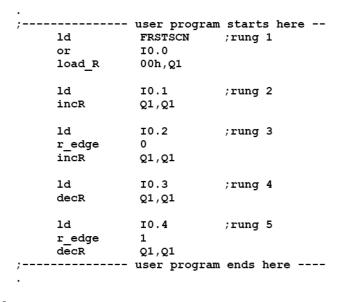

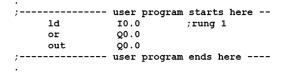

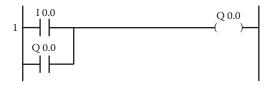

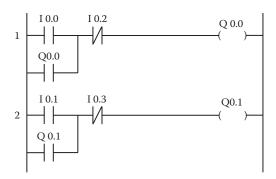

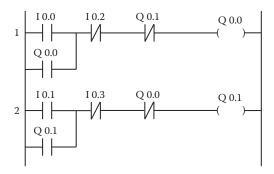

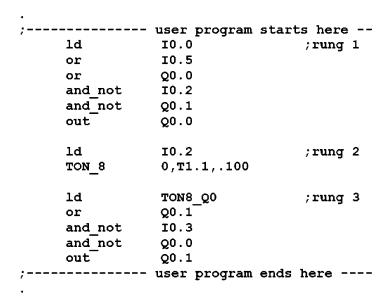

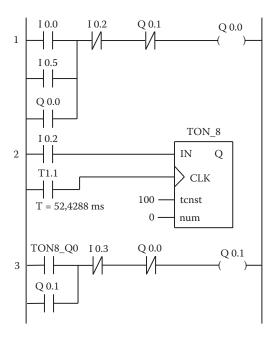

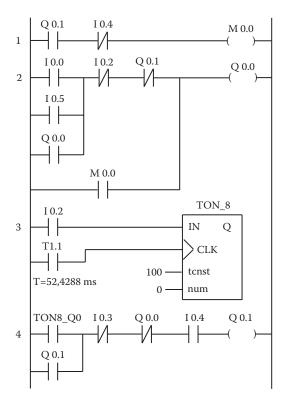

The basic software of the PIC16F648A-based PLC makes use of general purpose 8-bit registers of static random-access memory (SRAM) data memory of the PIC16F648A microcontroller. For the sake of simplicity, we restrict ourselves to use only BANK 0; i.e., all macros, including the basic definitions explained here, are defined by means of 8-bit SRAM registers of BANK 0. The file definitions.inc, included within the CD-ROM attached to this book, contains all basic macros and definitions necessary for the PIC16F648A-based PLC. In this chapter, we will explain the contents of this file. First, let us look at the file called UZAM\_plc\_16i16o\_ex1.asm, the view of which is shown in Figure 2.1. As is well known, a PLC scan cycle includes the following: obtain the inputs, run the user program, and update the outputs. This cycle is repeated as long as the PLC runs. Before getting into these endless PLC scan cycles, the initial conditions of the PLC are set up in the initialization stage. These main steps can be seen from Figure 2.1, where initialize is a macro for setting up the initial conditions, get inputs is a macro for getting and handling the inputs, and send outputs is a macro for updating the outputs. The user PLC program must be placed between get inputs and send outputs. The endless PLC scan cycles are obtained by means of the label "scan" and the instruction "goto scan."

The PIC16F648A-based PLC is fixed to run at 20 MHz with an external oscillator. The watchdog timer is used to prevent user program lockups. As

```

;Filename: UZAM_plc_16i16o_ex1.asm

;Date: 27 September 2011

;Author: Prof.Dr. Murat UZAM

;Company: Melikşah Üniversitesi

Mühendislik-Mimarlık Fakültesi

Elektrik-Elektronik Mühendisliği Bölümü

Talas, 38280, Kayseri, TURKEY

http://www.meliksah.edu.tr/muzam/

murat_uzam@meliksah.edu.tr

murat_uzam@hotmail.com

Tel: ++ 90 352 207 73 00 / 7351

Fax: ++ 90 352 207 73 49

;Notes: This is the basic program ; for PIC16F648A microcontroller

based UZAM PLC with

16 Inputs and 16 Outputs

and 32 Memory Bits (Internal Relays)

;-----;

list p=16F648A ;list directive to define processor #include <ple>plocessor specific variable definitions #include <definitions.inc> ;basic PLC definitions, macros, etc.

list

___CONFIG _ CP_OFF & DATA_CP_OFF & LVP_OFF & BOREN_OFF & _MCLRE_ON & _WDT_OFF & _PWRTE_ON & _HS_OSC

;Reset Vector

main

initialize

get inputs

----- user program starts here -----

;----- user program ends here -----

send outputs

goto scan

;directive 'end of program'

end

```

FIGURE 2.1 View of the file UZAM\_plc\_16i16o\_ex1.asm.

will be explained later, the hardware timer TMR0 is utilized to obtain freerunning reference timing signals.

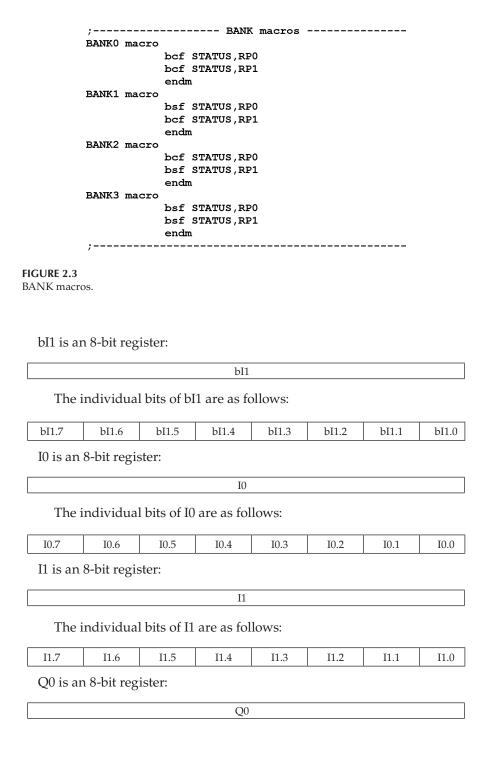

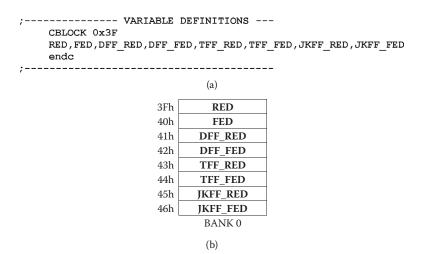

#### 2.1.1 Variable Definitions

Next, let us now consider the inside of the file definitions.inc. The definitions of 8-bit variables to be used for the basic software and their allocation in BANK 0 of SRAM data memory are shown in Figure 2.2(a) and (b), respectively. Although we can define as many inputs and outputs as we want, in this book we restrict ourselves to BANK 0 and define two 8-bit input registers and two 8-bit output registers (Q0 and Q1).

It is well known that inputs taken from contacts always suffer from contact bouncing. To circumvent this problem we define a debouncing mechanism for the inputs; this will be explained later. In the get\_inputs stage of the PLC scan cycle, the input signals are serially taken from the related 74HC/LS165 registers and stored in the SRAM registers. As a result, bI0 and bI1 will

hold these bouncing input signals. After applying the debouncing mechanism to the bouncing input signals of bI0 and bI1 we obtain debounced input signals, and they are stored in SRAM registers I0 and I1, respectively.

In the send\_outputs stage of the PLC scan cycle, the output information stored in the 8-bit SRAM registers Q0 and Q1 is serially sent out to and stored in the related TPIC6B595 registers. This means that Q0 and Q1 registers will hold output information, and they will be copied into the TPIC6B595 registers at the end of each PLC scan cycle. Four 8-bit registers, namely, M0, M1, M2, and M3, are defined for obtaining 32 memory bits (internal relays, in PLC jargon). To be used for the debouncer macros dbncr0 and dbncr1, we define sixteen 8-bit registers (DBNCR0, DBNCR0+1, ..., DBNCR0+7) and (DBNCR1, DBNCR1+1, ..., DBNCR1+7). In addition, the registers DBNCRRED0 and DBNCRRED1 are also defined to be used for the debouncer macros dbncr0 and dbncr1, respectively. Temp\_1 is a general temporary register declared to be used in the macros. Temp\_2 is declared to be used especially for obtaining special memory bits, as will be explained later. Timer\_2 is defined for storing the high byte of the free-running timing signals. The low byte of the free-running timing signals is stored in TMR0 (recalled as Timer\_1).

For accessing the SRAM data memory easily, BANK macros are defined as shown in Figure 2.3.

```

----- VARIABLE DEFINITIONS -----

CBLOCK 0x20

bI0,bI1

endc

CBLOCK 0x22

I0,I1

endc

CBLOCK 0x24

Q0,Q1

;

endc

CBLOCK 0x26

;4x8=32 Memory bits(Internal Relays)

M0,M1,M2,M3

CBLOCK 0x2A

;DBNCR0, DBNCR0+1, ..., DBNCR0+7

DBNCR0

endc

CBLOCK 0x32

DBNCR1

;DBNCR1, DBNCR1+1, ..., DBNCR1+7

endc

CBLOCK 0x3A

Temp_1,Temp_2,Timer_2,DBNCRRED0,DBNCRRED1

;-----

(a)

```

**FIGURE 2.2** (a) The definition of 8-bit variables to be used in the basic software. (*Continued*)

| 0.01 | 1.70      |

|------|-----------|

| 20h  | bI0       |

| 21h  | bI1       |

| 22h  | 10        |

| 23h  | I1        |

| 24h  | Q0        |

| 25h  | Q1        |

| 26h  | M0        |

| 27h  | M1        |

| 28h  | M2        |

| 29h  | М3        |

| 2Ah  | DBNCR0    |

| 2Bh  | DBNCR0+1  |

| 2Ch  | DBNCR0+2  |

| 2Dh  | DBNCR0+3  |

| 2Eh  | DBNCR0+4  |

| 2Fh  | DBNCR0+5  |

| 30h  | DBNCR0+6  |

| 31h  | DBNCR0+7  |

| 32h  | DBNCR1    |

| 33h  | DBNCR1+1  |

| 34h  | DBNCR1+2  |

| 35h  | DBNCR1+3  |

| 36h  | DBNCR1+4  |

| 37h  | DBNCR1+5  |

| 38h  | DBNCR1+6  |

| 39h  | DBNCR1+7  |

| 3Ah  | Temp_1    |

| 3Bh  | Temp_2    |

| 3Ch  | Timer_2   |

| 3Dh  | DBNCRRED0 |

| 3Eh  | DBNCRRED1 |

|      | BANK 0    |

|      | (b)       |

|      | (5)       |

# FIGURE 2.2 (Continued)

(b) Their allocation in BANK 0 of SRAM data memory.

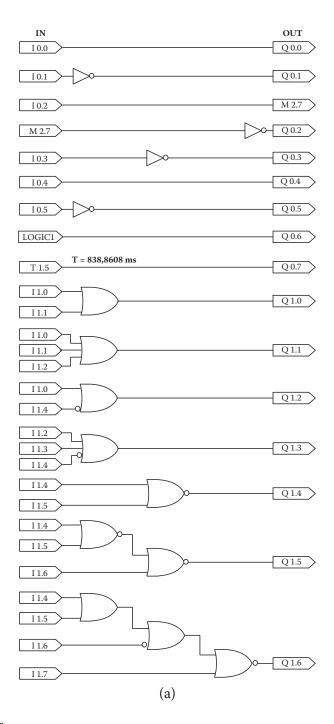

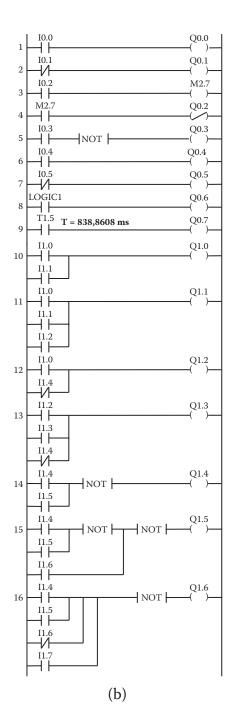

The definitions of 1-bit (Boolean) variables are depicted in Figure 2.4. The following definitions are self-explanatory: 74HC165, TPIC6B595, 16 INPUTS, 16 OUTPUTS, and 32 memory bits.

The individual bits (1-bit variables) of 8-bit SRAM registers bI0, bI1, I0, I1, Q0, Q1, M0, M1, M2, and M3 are shown below:

bI0 is an 8-bit register:

| bI0 |

|-----|

|     |

The individual bits of bI0 are as follows:

| bI0.7 | bI0.6 | bI0.5 | bI0.4 | bI0.3 | bI0.2 | bI0.1 | bI0.0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|-------|-------|-------|-------|-------|-------|-------|-------|

```

;----- 16 INPUTS -----

#define bI0.0 bI0,0

#define bI0.1 bI0,1

#define bI0.2 bI0,2

;b:bouncing

#define bI0.3 bI0,3

#define bI0.4 bI0,4

#define bI0.5 bI0,5

#define bI0.6 bI0,6

#define bI0.7 bI0,7

#define I0.0 I0,0

#define I0.1 I0,1

;I0 = debounced bI0

#define I0.2 I0,2

#define I0.3 I0,3

#define I0.4 I0.4

#define I0.5 I0,5

#define I0.6 I0,6

#define I0.7 I0,7

#define bI1.0 bI1,0

#define bI1.1 bI1,1

#define bI1.2 bI1,2

;b:bouncing

#define bI1.3 bI1,3

#define bI1.4 bI1,4

#define bI1.5 bI1,5

#define bI1.6 bI1,6

#define bI1.7 bI1,7

#define I1.0 I1,0

#define I1.1 I1,1

;I1 = debounced bI1

#define I1.2 I1,2

#define I1.3 I1,3

#define I1.4 I1,4

#define I1.5 I1,5

#define I1.6 I1,6

#define I1.7 I1,7

(a)

;----- 16 OUTPUTS -----

#define Q0.0 Q0,0

#define Q0.1 Q0,1

#define Q0.2 Q0,2

#define Q0.3 Q0,3

#define Q0.4 Q0,4

#define Q0.5 Q0,5

#define Q0.6 Q0,6

#define Q0.7 Q0,7

#define Q1.0 Q1,0

#define Q1.1 Q1,1

#define Q1.2 Q1,2

#define Q1.3 Q1,3

#define Q1.4

01,4

#define Q1.5 Q1,5

#define Q1.6 Q1,6

#define Q1.7 Q1,7

(b)

```

**FIGURE 2.4** Definitions of 1-bit (Boolean) variables: (a) 16 inputs, (b) 16 outputs. (*Continued*)

```

;----- LOGIC VALUES -----

#define LOGICO Temp_2,0

#define LOGIC1

Temp_2,1

;----- SPECIAL BITS -----

#define FRSTSCN Temp 2,2

#define SCNOSC

Temp 2,3

;-----

(c)

;----- Definitions for 74HC165 -----

#define data in PORTB,0

#define clock in PORTB,6

#define shft Id PORTB,7

;-----

;----- Definitions for TPIC6B595 -----

#define data out PORTB, 4

#define clock out PORTB, 3

#define latch out PORTB,5

;-----

(d)

```

#### FIGURE 2.4 (Continued)

Definitions of 1-bit (Boolean) variables: (c) logic values and special bits, (d) definitions for 74HC165 and TPIC6B595. (Continued)

The individual bits of Q0 are as follows:

| Q0.7                     | Q0.6                                      | Q0.5 | Q0.4 | Q0.3 | Q0.2 | Q0.1 | Q0.0 |  |

|--------------------------|-------------------------------------------|------|------|------|------|------|------|--|

| Q1 is an 8-bit register: |                                           |      |      |      |      |      |      |  |

|                          |                                           |      | Q1   |      |      |      |      |  |

| The i                    | The individual bits of Q1 are as follows: |      |      |      |      |      |      |  |

| Q1.7                     | Q1.6                                      | Q1.5 | Q1.4 | Q1.3 | Q1.2 | Q1.1 | Q1.0 |  |

| M0 is an                 | M0 is an 8-bit SRAM register:             |      |      |      |      |      |      |  |

| M0                       |                                           |      |      |      |      |      |      |  |

| ori ·                    | TI : 1: :1 11: (NO (1)                    |      |      |      |      |      |      |  |

The individual bits of M0 are as follows:

| M0.7 M0.6 M0.5 M0.4 | M0.3 M0.2 | M0.1 M0.0 |

|---------------------|-----------|-----------|

|---------------------|-----------|-----------|

M1 is an 8-bit SRAM register:

| M1 |

|----|

```

;--- 32 Memory Bits(Internal Relays) -----

#define M0.0 M0,0

#define M0.1 M0,1

#define M0.2 M0,2

#define M0.3 M0,3

#define M0.4 M0,4

#define M0.5 M0,5

#define M0.6 M0,6

#define M0.7 M0,7

#define M1.0 M1,0

#define M1.1 M1,1

#define M1.2 M1,2

#define M1.3 M1,3

#define M1.4 M1,4

#define M1.5 M1,5

#define M1.6 M1,6

#define M1.7 M1,7

#define M2.0 M2,0

#define M2.1 M2,1

#define M2.2 M2,2

#define M2.3 M2,3

#define M2.4 M2,4

#define M2.5 M2,5

#define M2.6 M2,6

#define M2.7 M2,7

#define M3.0 M3,0

#define M3.1 M3,1

#define M3.2 M3.2

#define M3.3 M3,3

#define M3.4 M3,4

#define M3.5 M3,5

#define M3.6 M3,6

#define M3.7 M3,7

;-----

(e)

```

#### FIGURE 2.4 (Continued)

Definitions of 1-bit (Boolean) variables: (e) 32 memory bits (internal relays). (Continued)

The individual bits of M1 are as follows:

| M1.7 M1.6 | M1.5 | M1.4 | M1.3 | M1.2 | M1.1 | M1.0 |

|-----------|------|------|------|------|------|------|

|-----------|------|------|------|------|------|------|

### M2 is an 8-bit SRAM register:

| M2 |  |

|----|--|

|----|--|

### The individual bits of M2 are as follows:

| M2.7 | M2.6 | M2.5 | M2.4 | M2.3 | M2.2 | M2.1 | M2.0 |

|------|------|------|------|------|------|------|------|

|------|------|------|------|------|------|------|------|

```

;----- REFERENCE TIMING SIGNALS -----

#define Timer_1 TMR0 ;at 20 MHz clock frequency:

#define T0.0 Timer_1,0 ;Timer clock : 0.1024 ms

#define T0.1 Timer 1,1 ;Timer clock :

0.2048 ms

#define T0.2 Timer 1,2 ;Timer clock :

0.4096 ms

#define T0.3 Timer 1,3 ;Timer clock :

0.8192 ms

#define T0.4 Timer 1,4 ;Timer clock :

1.6384 ms

#define T0.5 Timer_1,5 ;Timer clock :

3.2768 ms

#define T0.6 Timer_1,6 ;Timer clock :

6.5536 ms

#define T0.7 Timer 1,7 ;Timer clock : 13.1072 ms

#define T1.0 Timer 2,0 ;Timer clock : 26.2144 ms

#define T1.1 Timer 2,1 ;Timer clock :

52.4288 ms

#define T1.2 Timer 2,2 ;Timer clock :

104.8576 ms

#define T1.3 Timer 2,3 ;Timer clock :

209.7152 ms

#define T1.4 Timer 2,4 ; Timer clock : 419.4304 ms

#define T1.5 Timer_2,5 ;Timer clock : 838.8608 ms

#define T1.6 Timer_2,6 ;Timer clock : 1677.7216 ms = 1.6777216 s.

#define T1.7 Timer 2,7 ;Timer clock : 3355.4432 ms = 3.3554432 s.

(f)

```

#### FIGURE 2.4 (Continued)

Definitions of 1-bit (Boolean) variables: (f) 16 reference timing signals.

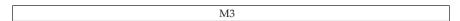

### M3 is an 8-bit SRAM register:

The individual bits of M3 are as follows:

Register Temp\_2 has the following individual bits:

| 7 | 6 | 5 | 4 | 3      | 2       | 1      | 0      |

|---|---|---|---|--------|---------|--------|--------|

|   |   |   |   | SCNOSC | FRSTSCN | LOGIC1 | LOGIC0 |

LOGIC0: Set to 0 after the first scan. LOGIC1: Set to 1 after the first scan.

FRSTSCN: Set to 1 during the first scan and set to 0 after the first scan.

SCNOSC: Toggled between 0 and 1 at each scan.

The variable LOGIC0 is defined to hold a logic 0 value throughout the PLC operation. At the initialization stage it is deposited with this value. Similarly, the variable LOGIC1 is defined to hold a logic 1 value throughout the PLC operation. At the initialization stage it is deposited with this value. The special memory bit FRSTSCN is arranged to hold the value of 1 at the first PLC scan cycle only. In the other PLC scan cycles following the first one it is reset. The special memory bit SCNOSC is arranged to work as a *scan oscillator*. This means that in one PLC scan cycle this special bit will hold the value of 0, in

the next one the value of 1, in the next one the value of 0, and so on. This will keep on going for every PLC scan cycle.

Timer\_1 (TMR0) is an 8-bit register:

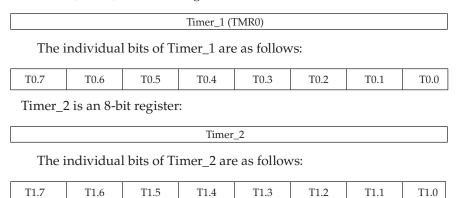

Let us now consider the 16 reference timing signals. As will be explained later, TMR0 of PIC16F648A is set up to count the ¼ of 20 MHz oscillator signal, i.e., 5 MHz with a prescaler arranged to divide the signal to 256. As a result, by means of TMR0 bits (also called Timer\_1), we obtain eight freerunning reference timing signals with the T timing periods starting from 0.1024 ms to 13.1072 ms. As will be explained later, the register Timer\_2 is incremented on Timer\_1 overflow. This also gives us (by means of Timer\_2 bits) eight more free-running reference timing signals with the T timing periods starting from 26.2144 ms to 3355.4432 ms. The timing diagram of the free-running reference timing signals is depicted in Figure 2.5. Note that the evaluation of TMR0 (Timer\_1) is independent from the PLC scan cycles, but Timer\_2 is incremented within the get\_inputs stage of the PLC scan cycle on Timer\_1 overflow. This is justified as long as the PLC scan cycle takes less than 13.1072 ms.

**FIGURE 2.5** Timing diagram of the free-running reference timing signals (T = 0.1024, 0.2048, ..., 3355.4432 ms).

```

;----- Macro HC165 -----

HC165

macro num, var0

;This macro can be used for 74HC/HCT/LS165

local i=0,j=0

parallel to serial shift register ICs;

;latch

;the inputs

bcf shft_ld

nop

shft ld

;of all 74HC165s

bsf

num ;carry on while j < num

i < 8 ;for each 74HC165, 8 times do the following

var0+j,f ;rotate the register "var0+j" one position left

data_in ;if the data_in is set then skip

while j < \overline{num}

while i < 8

rlf

btfss data in

bcf var0+j,0 ;if the data in is reset then reset "var0+j,0"

btfsc data in ;if the data in is reset then skip

bsf var0+j,0 ;if the data in is set then set "var0+j,0"

;generate

clock_in

bcf

nop

;a clock in

bsf clock in

;pulse

i += 1

;increment "i"

endw

;after 8 iterations end the while loop for "i"

i=0

;i=0 : get ready

;increment "j" : for a new 74HC165

j += 1

;after 'num' iterations end the while loop for "j"

endw

endm

;end macro HC165

```

FIGURE 2.6 The macro HC165.

#### 2.1.2 Macro HC165

The macro HC165 is shown in Figure 2.6. The input signals are serially taken from the related 74HC/LS165 registers and stored in the SRAM registers bIO and bII by means of this macro. The num defines the number of 74HC/LS165 registers to be considered. This means that with this macro we can obtain inputs from as many 74HC/LS165 registers as we wish. However, as explained before, in this book we restrict this number to be 2, because we have 16 discrete inputs. varO is the beginning of the registers to which the state of inputs taken from 74HC/LS165 registers will be stored. This implies that there should be enough SRAM locations reserved after varO, and also there should be enough 74HC/LS165 registers to get the inputs from. There are some explanations within the macro to describe how it works. As can be seen, this macro makes use of previously defined data\_in, clock\_in, and sfht ld bits to obtain the input signals from 74HC/LS165 registers.

### 2.1.3 Macro HC595

The macro HC595 is shown in Figure 2.7. The output signals are stored in the 8-bit SRAM registers Q0 and Q1 and serially sent out to and stored in the related TPIC6B595 registers by means of this macro. The num defines the number of TPIC6B595 registers to be used. This means that with this macro we can send output data serially to as many TPIC6B595 registers as we wish. However as explained before, in this book we restrict this number to 2, because we have 16 discrete outputs. var0 is the beginning of the 8-bit registers, such as Q0 in SRAM from which the state of outputs are taken and serially sent out to TPIC6B595 registers. This implies that there should

```

;----- Macro HC595 -----

macro num,var0 ;This macro can be used for 74HC/HCT/LS595

local i=0,j=num-1 ;or TPIC6B595 serial to parallel shift register ICs

while j >= 0 ;carry on while j >= 0

while i < 8 ;for each TPIC6B595, 8 times do the following:

rlf var0+j,f ;rotate the register "var0+j" one position left

btfss STATUS,C ;if the Carry flag is set then skip

HC595

macro num, var0

data out ;if the Carry flag is reset then reset data out

bcf

btfsc STATUS,C

;if the Carry flag is reset then skip

data_out

;if the Carry flag is set then set data out

bsf

clock_out ;generate

nop

;a clock out

clock out ;pulse

;increment "i"

i += 1

endw

;after 8 iterations end the while loop for "i"

rlf var0+j,f

;rotate the register "var0+j" one position left

i=0

: get ready

decrement "j" : for a new TPIC6B595

j-= 1

;after 'num' iterations end the while loop for "j"

endw

bsf

latch out

;Latch the serially shifted out data

nop

on all

latch_out

;TPIC6B595's

bcf

;end macro HC595

endm

```

FIGURE 2.7 The macro HC595.

be enough SRAM locations reserved after var0, and also there should be enough TPIC6B595 registers to hold the outputs. There are some explanations within the macro to describe how it works. As can be seen, this macro makes use of previously defined data\_out, clock\_out, and latch\_out bits to send the output signals serially to TPIC6B595 registers.

# 2.2 Elimination of Contact Bouncing Problem in the PIC16F648A-Based PLC

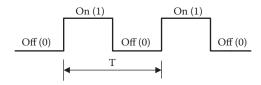

# 2.2.1 Contact Bouncing Problem

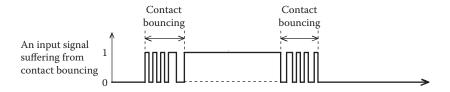

When a mechanical contact, such as a push-button switch, examples of which are shown in Figure 2.8, user interface button, limit switch, relay, or contactor contact, is opened or closed, the contact seldom demonstrates a clean transition from one state to another. There are two types of contacts: normally open (NO) and normally closed (NC). When a contact is closed or opened, it will close and open (technically speaking, make and break) many times before finally settling in a stable state due to mechanical vibration. As can be seen from Figure 2.9, this behavior of a contact is interpreted as multiple false input signals, and a digital circuit will respond to each of these on-off or off-on transitions. This problem is well known as *contact bounce* and has always been a very important problem when interfacing switches, relays, etc., to a digital control system.

**FIGURE 2.8** Different types and makes of switches and buttons.

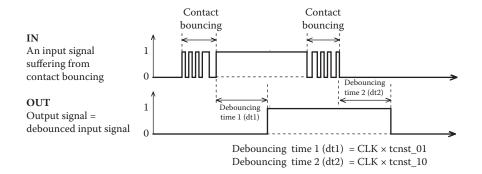

In some industrial applications *debouncing* is required to eliminate both mechanical and electrical effects. Most switches seem to exhibit bounce duration under 10 ms, and therefore it is reasonable to pick a debounce period in the 20 to 50 ms range. On the other hand, when dealing with relay contacts, the debounce period should be large enough, i.e., within the 20 to 200 ms range. Nevertheless, a reasonable switch will not bounce longer than 500 ms. Both closing and opening contacts suffer from the bouncing problem, and therefore in general, both rising and falling edges of an input signal should be debounced, as seen from the timing diagram of Figure 2.10.

**FIGURE 2.9** Contact bouncing problem, causing an input signal to bounce between 0 and 1.

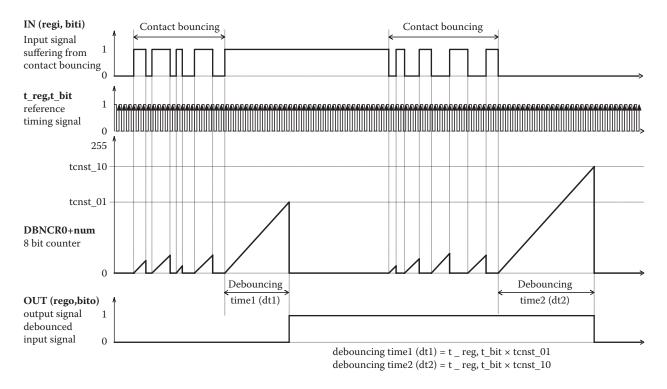

FIGURE 2.10

The timing diagram of a single I/O debouncer (also the timing diagram of each channel of the independent 8-bit I/O contact debouncers, dbncr0 and dbncr1).

# 2.2.2 Understanding a Generic Single I/O Contact Debouncer

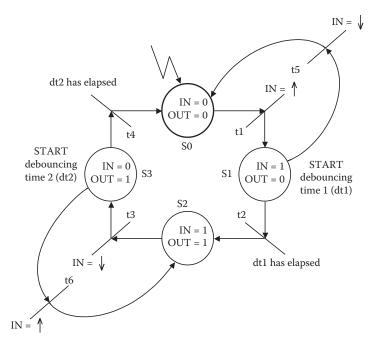

In order to understand how a debouncer works, let us now consider a generic single I/O debouncer. We can think of the generic single I/O debouncer as being a single INput/single OUTput system, whose state transition diagram is shown in Figure 2.11. In the state transition diagram there are four states,

**FIGURE 2.11** State transition diagram of a generic single I/O debouncer.

S0, S1, S2, and S3, drawn as circles, and six transitions, t1, t2, ..., t6, drawn as bars. States and transitions are connected by directed arcs. The following explains the behavior of the generic single I/O debouncer (also each channel of the independent 8-bit I/O contact debouncers, dbncr0 and dbncr1) based on the state transition diagram shown in Figure 2.11:

- 1. Initially, it is assumed that the input signal IN and the output signal OUT are both LOW (state S0).

- 2. When the system is in S0 (the IN is LOW and the OUT is LOW), if the rising edge (↑) of IN is detected (transition t1), then the system moves from S0 to S1 and the debouncer starts a time delay, called debouncing time 1 (dt1).

- 3. While the system is in S1 (the IN is HIGH and the OUT is LOW), before the dt1 ms time delay ends, if the falling edge (↓) of IN is detected (transition t5), then the system goes back to S0 from S1, and the time delay dt1 is canceled and the OUT remains LOW (no state change is issued).

- 4. When the system is in S1 (the IN is HIGH and the OUT is LOW), if the input signal is still HIGH and the time delay dt1 has elapsed (transition t2), then the system moves from S1 to S2. In this case, the state change is issued, i.e., the OUT is set to HIGH.

- 5. When the system is in S2 (the IN is HIGH and the OUT is HIGH), if the falling edge (↓) of IN is detected (transition t3), then the system moves from S2 to S3 and the debouncer starts a time delay, called debouncing time 2 (dt2).

- 6. While the system is in S3 (the IN is LOW and the OUT is HIGH), before the dt2 ms time delay ends, if the rising edge (↑) of IN is detected (transition t6), then the system goes back to S2 from S3, and the time delay dt2 is canceled and the OUT remains HIGH (no state change is issued).

- 7. When the system is in S3 (the IN is LOW and the OUT is HIGH), if the input signal is still LOW and the time delay dt2 has elapsed (transition t4), then the system moves from S3 to S0. In this case, the state change is issued, i.e., the OUT is set to LOW.

### 2.2.3 Debouncer Macros dbncr0 and dbncr1

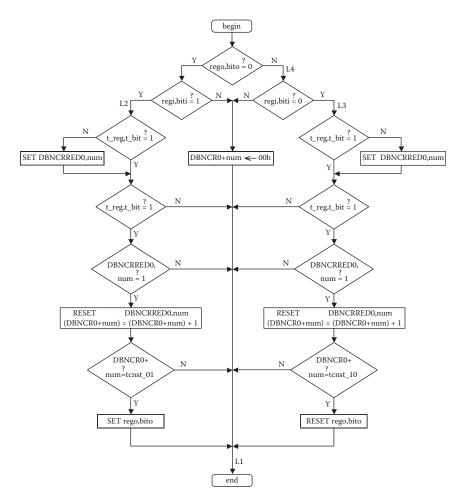

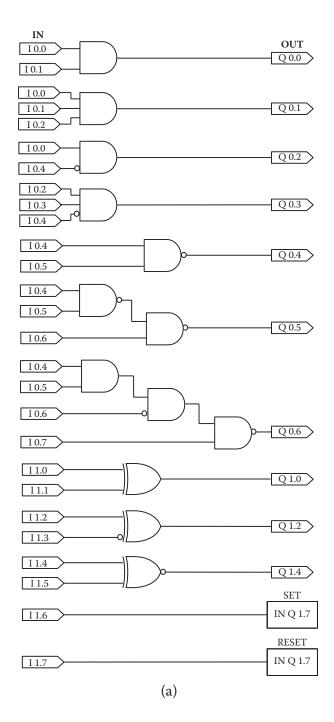

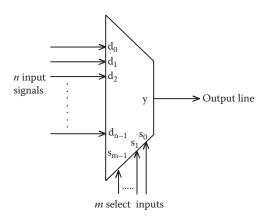

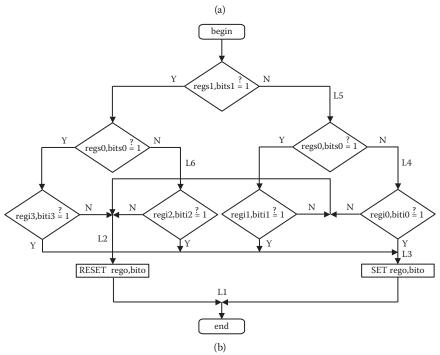

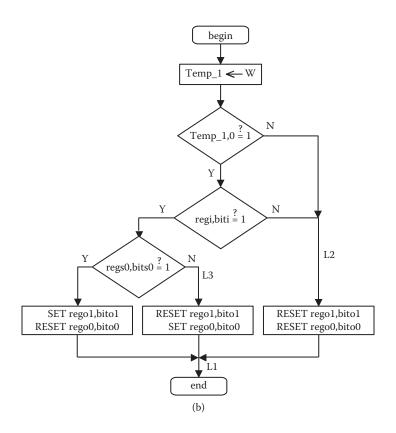

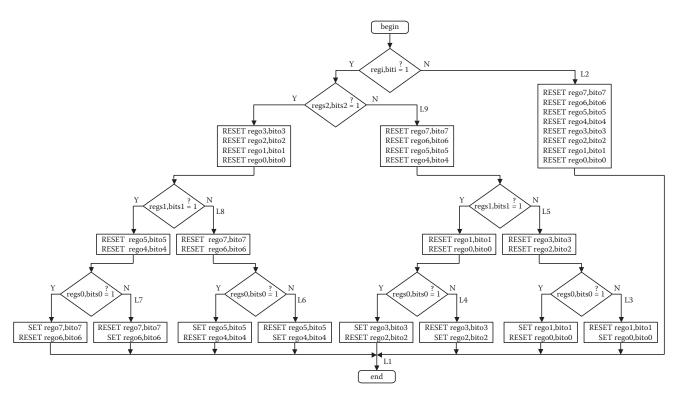

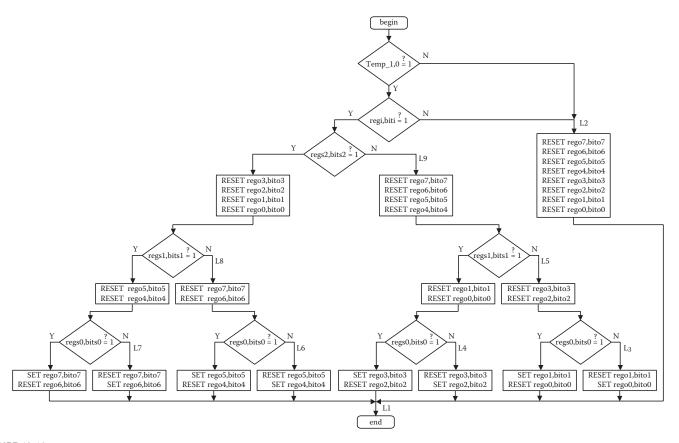

The macro dbncr0 and its flowchart are shown in Figures 2.12 and 2.13, respectively. Table 2.1 shows the schematic symbol of the macro dbncr0. The detailed timing diagram of one channel of this debouncer is provided in Figure 2.14. It can be used for debouncing eight independent buttons, switches, relay or contactor contacts, etc. It is seen that the output changes its state only after the input becomes stable and waits in the stable state for the

```

;----- macro: debouncer0 ------

dbncr0 macro num, reqi, biti, t req, t bit, tcnst 01, tcnst 10, reqo, bito

local L1, L2, L3, L4

btfsc rego,bito

goto

L4

btfsc regi,biti

goto

L2

clrf

DBNCR0+num

goto

L4

btfss regi,biti

goto

L3

clrf

DBNCR0+num

goto

L1

L3

btfss t reg,t bit

DBNCRRED0, num

btfss t_reg,t_bit

goto

L1

btfss DBNCRRED0, num

goto

L1

bcf

DBNCRRED0, num

incf

DBNCR0+num, f

movf DBNCR0+num, i

xorlw tcnst 10

skpnz

rego,bito

bcf

aoto

L1

L2

btfss

t reg,t bit

DBNCRRED0, num

bsf

btfss t reg,t bit

L1

goto

btfss

DBNCRRED0, num

goto

DBNCRRED0, num

bcf

incf DBNCR0+num,f

movf DBNCR0+num.

xorlw tcnst 01

skpnz

bsf

rego,bito

L1

endm

;-----

```

# FIGURE 2.12 The macro dbncr0.

predefined debouncing time dt1 or dt2. The debouncing is applied to both rising and falling edges of the input signal. In this macro, each channel is intended for a *normally open contact* connected to the PIC by means of a pull-down resistor, as this is the case with the PIC16F648A-based PLC. It can also be used without any problem for a *normally closed contact* connected to the PIC by means of a pull-up resistor. The debouncing times, such as 20, 50, or 100 ms, can be selected as required depending on the application. It is possible to pick up different debouncing times for each channel. It is also possible to choose different debouncing times for rising and falling edges of the same input signal if necessary. This gives a good deal of flexibility. This is simply

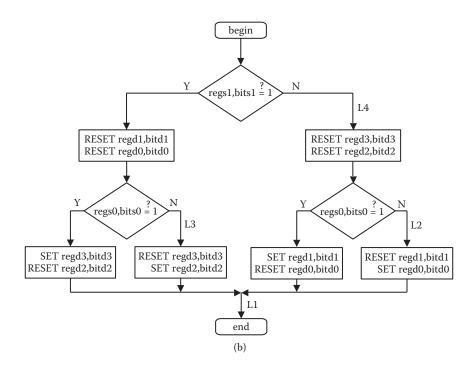

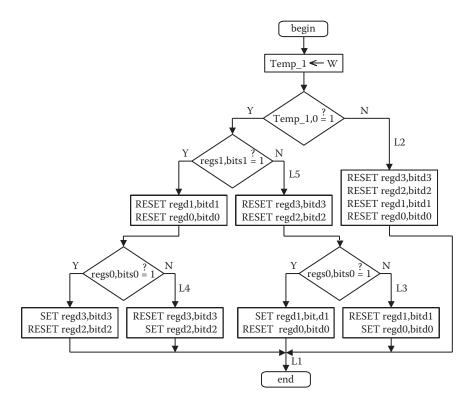

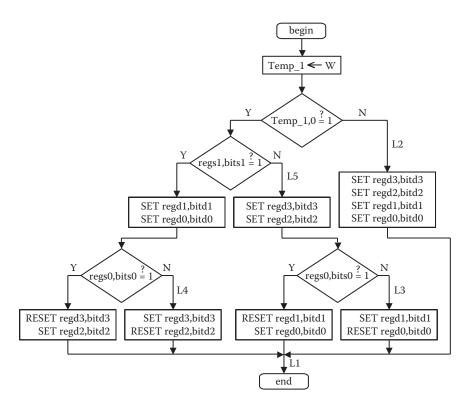

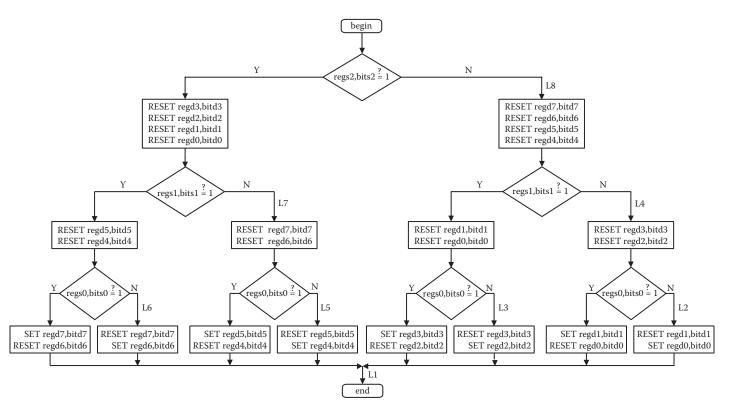

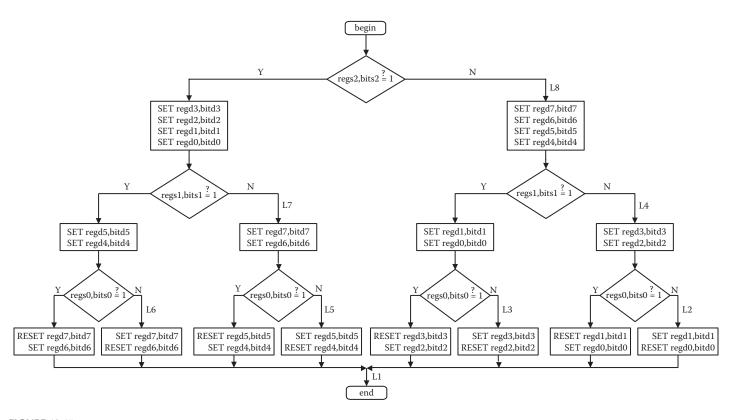

FIGURE 2.13

The flowchart of the macro dbncr0.

done by changing the related time constant tcnst\_01 or tcnst\_10 defining the debouncing time delay for each channel and for both edges within the assembly program. Note that if the state change of the contact is shorter than the predefined debouncing time, this will also be regarded as bouncing, and it will not be taken into account. Therefore, no state change will be issued in this case. Each of the eight input channels of the debouncer may be used independently from other channels. The activity of one channel does not affect that of the other channels.

Let us now briefly consider how the macro dbncr0 works. First, one of the previously defined reference timing signals is chosen as t\_reg,t\_bit, to be used within this macro. Then, we can set up both debouncing times dt1 and dt2 by means of time constants tcnst\_01 and tcnst\_10, as

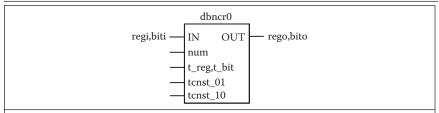

**TABLE 2.1**Schematic Symbol of the Macro dbncr0

IN (regi,biti): A Boolean variable passed into the macro through regi,biti.

It represents the input signal to be debounced.

**num**: Any number from 0 to 7. Eight independent debouncers are chosen by this number. It is used to define the 8-bit variable "DBNCR0+num" and the edge detector bit "DBNCRRED0,num."

t\_reg,t\_bit: One of the reference timing signals T0.0, T0.1, ..., T0.7, T1.0, T1.1, ..., T1.7. It defines the timing period.

**tcnst\_01**: An integer constant value from 1 to 255. Debouncing time 1 **(dt1)** is obtained by this formula:  $dt1 = the period of (t_reg,t_bit) \times tcnst_01$ .

**tcnst**\_10: An integer constant value from 1 to 255. Debouncing time 2 (**dt2**) is obtained by this formula:  $dt2 = the period of (t_reg,t_bit) \times tcnst_10$ .

**OUT(rego,bito)**: A Boolean variable passed out of the macro through rego,bito. It represents the output signal, which is the debounced version of the input signal.

dt1 = the period of (t\_reg,t bit) × tcnst 01 and dt2 = the period of (t reg, t bit) × tcnst 10, respectively. If the input signal (regi, biti) = 0 and the output signal (rego, bito) = 0 or the input signal (regi, biti) = 1 and the output signal (rego, bito) = 1, then the related counter DBNCR0+num is loaded with 00h and no state change is issued. If the output signal (rego, bito) = 0 and the input signal (regi, biti) = 1, then with each rising edge of the reference timing signal t req,t bit the related counter DBNCR0+num is incremented by one. In this case, when the count value of DBNCR0+num is equal to the number tcnst 01, this means that the input signal is debounced properly and then state change from 0 to 1 is issued for the output signal (rego, bito). Similarly, if the output signal (rego, bito) = 1 and the input signal (regi, biti) = 0, then with each rising edge of the reference timing signal t reg, t bit the related counter DBNCR0+num is incremented by one. In this case, when the count value of DBNCR0+num is equal to the number tcnst 10, this means that the input signal is debounced properly and then state change from 1 to 0 is issued for the output signal (rego, bito). For this macro it is necessary to define the following 8-bit variables in SRAM: Temp\_1 and DBNCRRED0. In addition, it is also necessary to define eight 8-bit variables in successive SRAM locations, the first of which is to be defined as DBNCR0. It is not necessary to name the other seven variables. Each bit of the variable DBNCRRED0 is used to detect the rising edge of the reference timing signal t reg, t bit for the related channel.

**FIGURE 2.14**Detailed timing diagram of one of the channels of the macro dbncr0.

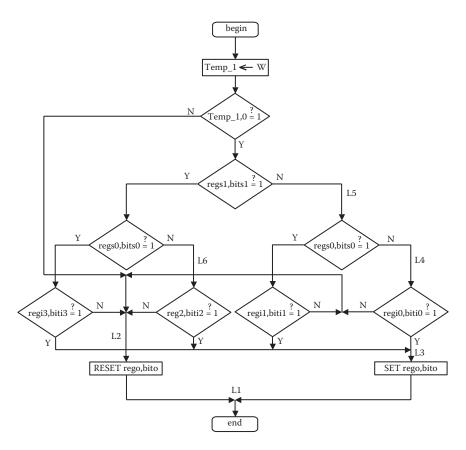

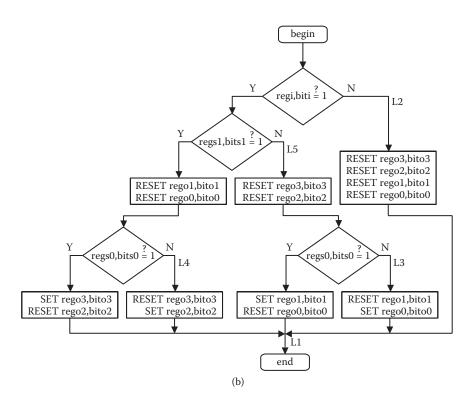

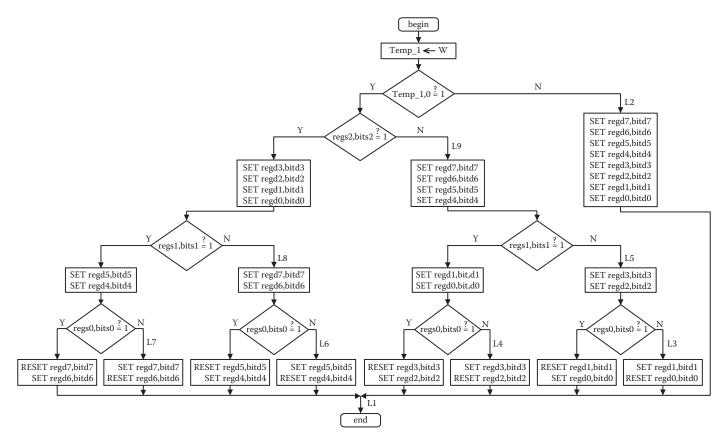

With the use of the macro dbncr0 it is possible to debounce 8 input signals; as we commit to have 16 discrete inputs in the PIC16F648A-based PLC project, there are 8 more input signals to be debounced. To solve this problem the macro dbncr1 is introduced. It works in the same manner as the macro dbncr0. The macro dbncr1 is shown in Figure 2.15. Table 2.2 shows the schematic symbol of the macro dbncr1. For this macro it is necessary to define the following 8-bit variables in SRAM: Temp\_1 and DBNCRRED1. Each bit of the variable DBNCRRED1 is used to detect the rising edge of the reference timing signal t reg, t bit for the related channel. In addition, it

```

;----- macro: debouncer1 ------

dbncrl macro num, regi, biti, t reg, t bit, tcnst 01, tcnst 10, rego, bito

local L1, L2, L3, L4

btfsc rego,bito

L4

goto

btfsc regi,biti

goto

L2

clrf

DBNCR1+num

goto

L1

L4

btfss regi,biti

goto L3

DBNCR1+num

clrf

goto

L1

L3

btfss t reg,t bit

DBNCRRED1, num

btfss

t_reg,t_bit

L1

goto

btfss

DBNCRRED1, num

goto

bcf

DBNCRRED1, num

incf

DBNCR1+num, f

movf

DBNCR1+num, w

xorlw tcnst 10

skpnz

bcf

rego,bito

goto

L1

L2

btfss t reg,t bit

bsf

DBNCRRED1, num

btfss t reg,t_bit

goto

L1

btfss

DBNCRRED1, num

goto

L1

bcf

DBNCRRED1, num

DBNCR1+num,f

incf

movf

DBNCR1+num,w

xorlw tcnst 01

skpnz

bsf

rego,bito

L1

endm

;-----

```

FIGURE 2.15

The macro dbncr1.

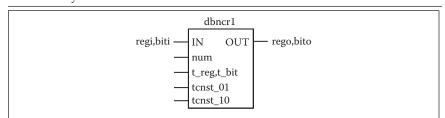

**TABLE 2.2**Schematic Symbol of the Macro dbncr1

**IN** (**regi,biti**): A Boolean variable passed into the macro through regi,biti. It represents the input signal to be debounced.

**num**: Any number from 0 to 7. Eight independent debouncers are chosen by this number. It is used to define the 8-bit variable "DBNCR1+num" and the edge detector bit "DBNCRRED1,num."

**t\_reg,t\_bit**: One of the reference timing signals T0.0, T0.1, ..., T0.7, T1.0, T1.1, ..., T1.7. It defines the timing period.

tcnst\_01: An integer constant value from 1 to 255. Debouncing time 1 (dt1) is obtained by this formula: dt1 = the period of (t\_reg,t\_bit) × tcnst\_01.

**tcnst**\_10: An integer constant value from 1 to 255. Debouncing time 2 (**dt2**) is obtained by this formula:  $dt2 = the period of (t_reg,t_bit) \times tcnst_10$ .

**OUT(rego,bito)**: A Boolean variable passed out of the macro through rego,bito. It represents the output signal, which is the debounced version of the input signal.

is also necessary to define eight 8-bit variables in successive SRAM locations, the first of which is to be defined as DBNCR1.

### 2.3 Basic Macros of the PIC16F648A-Based PLC

In this section the following basic three macros are considered: initialize, get\_inputs, and send\_outputs.

### 2.3.1 Macro initialize

The macro initialize is shown in Figure 2.16. There are mainly two tasks carried out within this macro. In the former, first, TMR0 is set up as a free-running hardware timer with the ¼ of 20 MHz oscillator signal, i.e., 5 MHz, and with a prescaler arranged to divide the signal to 256. In addition, PORTB is initialized to make RB0 (data\_in) as input, and the following as outputs: RB3 (clock\_out), RB4 (data\_out), RB5 (latch\_out), RB6 (clock\_in), and RB7 (shift/load). In the latter, all utilized SRAM registers are loaded with initial "safe values." In other words, all utilized SRAM registers are cleared (loaded with 00h) except for Temp\_2, which is loaded with 06h.

```

;----- macro: initialize -----

initialize macro

local

goto BANK1;

BANK1

BANK1 ;goto BANK1

movlw b'00000111' ; W <-- b'00000111' : Fosc/4 --> TMR0

movwf OPTION_REG ;pull-up on PORTB, OPTION_REG <-- W

movlw b'00000001' ;PORTB is both input and output port

;W <-- b'00000111' : Fosc/4 --> TMR0, PS=256

;TRISB <-- b'00000001'

movwf

TRISB

;goto BANKO

BANKO

clrf

PORTA

;Clear PortA

clrf

PORTB

;Clear PortB

TMR0

clrf

;Clear TMR0

movlw h'20'

;initialize the pointer

movwf FSR

to RAM

L1

INDF

;clear INDF register

clrf

FSR,f

incf

;increment pointer

btfss FSR,7

;all done?

;if not goto L1

goto

;if yes carry on

06h

Temp_2

;W <--- 06h

movlw

movwf

;Temp_2 <--- W(06h)

endm

;-----

```

FIGURE 2.16

The macro initialize.

As explained before, Temp\_2 holds some special memory bits; therefore, the initial values of these special memory bits are put into Temp\_2 within this macro. As a result, these special memory bits are loaded with the following initial values: LOGIC0 (Temp\_2,0) = 0, LOGIC1 (Temp\_2,1) = 1, FRSTSCN (Temp\_2,2) = 1, SCNOSC (Temp\_2,3) = 0.

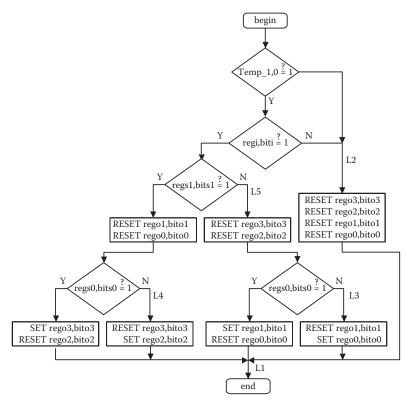

### 2.3.2 Macro get inputs

The macro get inputs is shown in Figure 2.17. There are mainly three tasks carried out within this macro. In the first one, the macro HC165 is called with the parameters .2 and bIO. This means that we will use the CPU board and two I/O extension boards; therefore, the macro HC165 is called with the parameter .2. As explained before, the input information taken from the macro is rated as bouncing information, and therefore these 16-bit data are stored in bI0 and bI1 registers. For example, if we decide to use the CPU board connected to four I/O extension boards, then we must call the macro HC165 as follows: HC165.4, bIO. Then, this will take four 8-bit bouncing input data from the 74HC/LS165 ICs and put them to the four successive registers starting with the register bIO. In the second task within this macro, each bit of bI0,i (i = 0, 1, ..., 7) is debounced by the macro dbncr0, and each debounced input signal is stored in the related bit I0,i (i = 0, 1, ..., 7). Likewise, each bit of  $bI1_i$  (i = 0, 1, ..., 7) is debounced by the macro dbncr1, and each debounced input signal is stored in the related bit I1, i (i = 0, 1, ..., 7). In general, a 10 ms time delay is enough for debouncing both rising and falling edges of an input signal. Therefore, to achieve these time delays, the

```

;----- macro: get_inputs ------

get_inputs macro

local

Nzero

; obtain the 16 inputs from

HC165

.2,bI0

dbncr0 0,bI0.0,T0.2,.25,.25,I0.0 ;2 input registers (74HC165)

dbncr0 1,bI0.1,T0.2,.25,.25,I0.1 ;and put them into bI0 and bI1

dbncr0 2,bI0.2,T0.2,.25,.25,I0.2 ;registers within PIC16F648A.

dbncr0 3,bI0.3,T0.2,.25,.25,I0.3

;Then debounce all bits of

dbncr0 4,bI0.4,T0.2,.25,.25,I0.4

;bI0.

dbncr0

5,bI0.5,T0.2,.25,.25,I0.5

;The debounced input signals

dbncr0 6,bI0.6,T0.2,.25,.25,I0.6

; are stored in the register

dbncr0 7,bI0.7,T0.2,.25,.25,I0.7

;10

;dt1=dt2=0.4096 \text{ ms } \times 25 = 10,24 \text{ ms}

dbncr1 0,bI1.0,T0.2,.25,.25,I1.0

;Likewise debounce all bits of

dbncr1 1,bI1.1,T0.2,.25,.25,I1.1

dbncr1 2,bI1.2,T0.2,.25,.25,I1.2

;bI1.

dbncr1 3,bI1.3,T0.2,.25,.25,I1.3

dbncr1 4,bI1.4,T0.2,.25,.25,I1.4

dbncr1 5,bI1.5,T0.2,.25,.25,I1.5

;The debounced input signals

dbncrl 6,bI1.6,T0.2,.25,.25,I1.6

; are stored in the register

dbncr1 7,bI1.7,T0.2,.25,.25,I1.7

btfsc

Timer 1,7

Temp \overline{2}, 4

;Increment Timer 2 on Timer 1 overflow

bsf

btfsc Timer_1,7

Nzero

goto

btfss

Temp_2, 4

goto

Nzero

Timer 2,f

incf

Temp \frac{1}{2}, 4

Nzero

endm

```

FIGURE 2.17

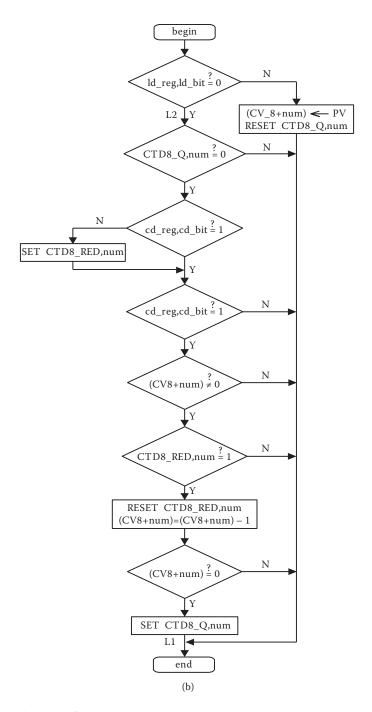

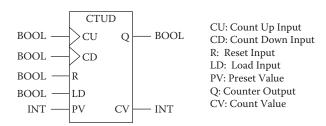

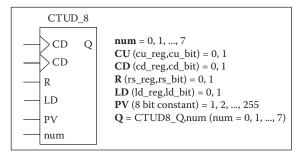

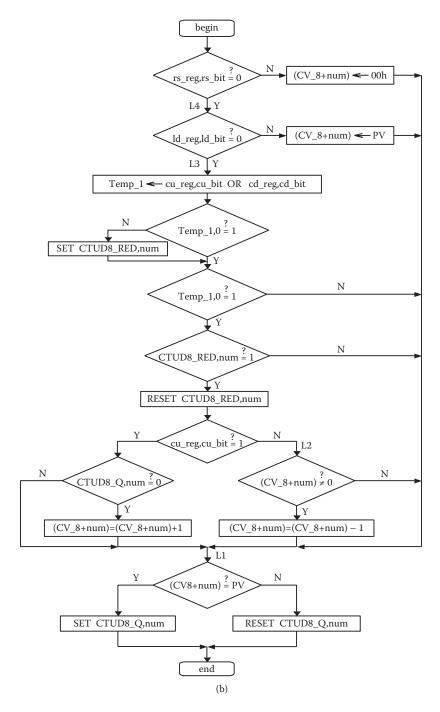

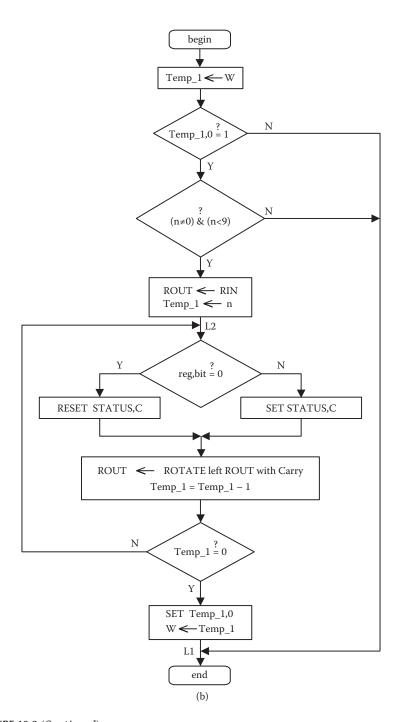

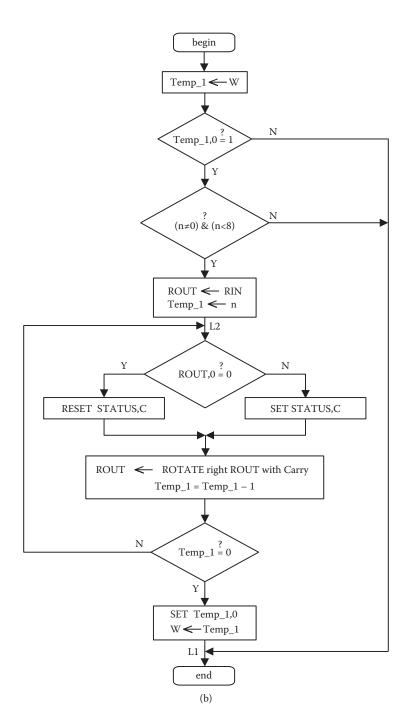

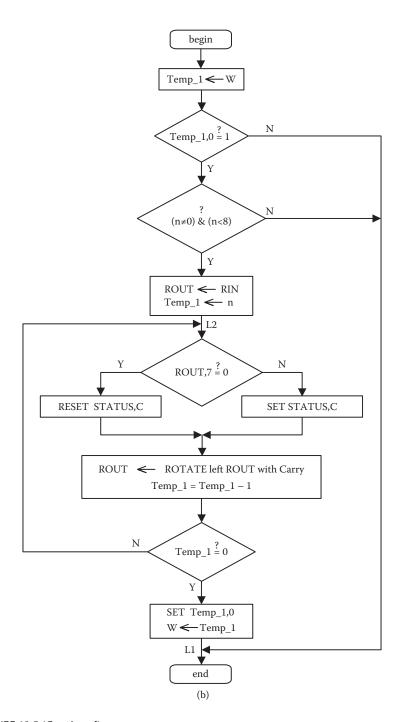

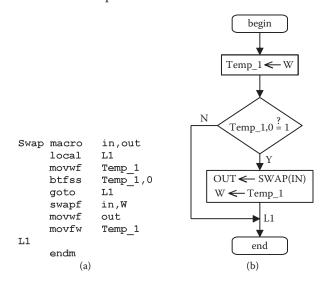

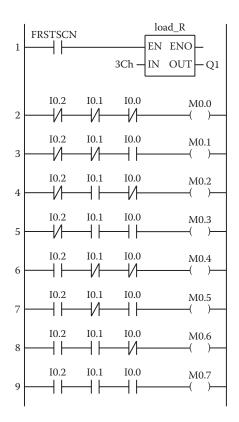

The macro get\_inputs.