Introduction to Low Level Programming for Microprocessors J. C. Cluley

# **Macmillan Computer Science Series**

Consulting Editor

Professor F.H. Sumner, University of Manchester

S.T. Allworth and R.N. Zobel, Introduction to Real-time Software Design, second edition

Ian O. Angell and Gareth Griffith, High-resolution Computer Graphics Using FORTRAN 77

Ian O. Angell and Gareth Griffith, High-resolution Computer Graphics Using Pascal

M.A. Azmoodeh, Abstract Data Types and Algorithms

C. Bamford and P. Curran, Data Structures, Files and Databases

Philip Barker, Author Languages for CAL

A.N. Barrett and A.L. Mackay, Spatial Structure and the Microcomputer

R.E. Berry and B.A.E. Meekings, A Book on C

G.M. Birtwistle, Discrete Event Modelling on Simula

T.B. Boffey, Graph Theory in Operations Research

Richard Bornat, Understanding and Writing Compilers

Linda E.M. Brackenbury, Design of VLSI Systems - A Practical Introduction

J.K. Buckle, Software Configuration Management

W.D. Burnham and A.R. Hall, Prolog Programming and Applications

J.C. Cluley, An Introduction to Low Level Programming for Microprocessors

J.C. Cluley, Interfacing to Microprocessors

Robert Cole, Computer Communications, second edition

Derek Coleman, A Structured Programming Approach to Data

Andrew J.T. Colin, Fundamentals of Computer Science

Andrew J.T. Colin, Programming and Problem-solving in Algol 68

S.M. Deen, Fundamentals of Data Base Systems

S.M. Deen, Principles and Practice of Database Systems

Tim Denvir, Introduction to Discrete Mathematics for Software Engineering

P.M. Dew and K.R. James, Introduction to Numerical Computation in Pascal

M.R.M. Dunsmuir and G.J. Davies, Programming the UNIX System

K.C.E. Gee, Introduction to Local Area Computer Networks

J.B. Gosling, Design of Arithmetic Units for Digital Computers

Roger Hutty, Z80 Assembly Language Programming for Students

Roland N. Ibbett, The Architecture of High Performance Computers

Patrick Jaulent, The 68000 - Hardware and Software

J.M. King and J.P. Pardoe, Program Design Using JSP - A Practical Introduction

H. Kopetz, Software Reliability

E.V. Krishnamurthy, Introductory Theory of Computer Science

V.P. Lane, Security of Computer Based Information Systems

Graham Lee, From Hardware to Software – an introduction to computers

A.M. Lister, Fundamentals of Operating Systems, third edition

(continued overleaf)

G.P. McKeown and V.J. Rayward-Smith, Mathematics for Computing

Brian Meek, Fortran, PL/1 and the Algols

Barry Morrell and Peter Whittle, CP/M 80 Programmer's Guide

Derrick Morris, System Programming Based on the PDP11

Pim Oets, MS-DOS and PC-DOS - A Practical Guide

Christian Queinnec, LISP

Gordon Reece, Microcomputer Modelling by Finite Differences

W.P. Salman, O. Tisserand and B. Toulout, FORTH

L.E. Scales, Introduction to Non-linear Optimization

Peter S. Sell, Expert Systems - A Practical Introduction

Colin J. Theaker and Graham R. Brookes, A Practical Course on Operating Systems

J-M. Trio, 8086-8088 Architecture and Programming

M.J. Usher, Information Theory for Information Technologists

B.S. Walker, Understanding Microprocessors

Peter J.L. Wallis, Portable Programming

Colin Walls, Programming Dedicated Microprocessors

I.R. Wilson and A.M. Addyman, A Practical Introduction to Pascal – with BS6192, second edition

#### Non-series

Roy Anderson, Management, Information Systems and Computers

- J.E. Bingham and G.W.P. Davies, A Handbook of Systems Analysis, second edition

- J.E. Bingham and G.W.P. Davies, Planning for Data Communications

# An Introduction to Low Level Programming for Microprocessors

J.C. Cluley

M.Sc., C. Eng., M.I.E.E., F.B.C.S.

All rights reserved. No reproduction, copy or transmission of this publication may be made without written permission.

No paragraph of this publication may be reproduced, copied or transmitted save with written permission or in accordance with the provisions of the Copyright Act 1956 (as amended), or under the terms of any licence permitting limited copying issued by the Copyright Licensing Agency, 33-4 Alfred Place, London WC1E 7DP.

Any person who does any unauthorised act in relation to this publication may be liable to criminal prosecution and civil claims for damages.

First published 1987

Published by

MACMILLAN EDUCATION LTD

Houndmills, Basingstoke, Hampshire RG21 2XS

and London

Companies and representatives

throughout the world

British Library Cataloguing in Publication Data Cluley, J.C.

An introduction to low level programming for microprocessors. — (Macmillan computer science series).

- 1. Microprocessors Programming

- I. Title

005.2'6 QA76.6

ISBN 978-0-333-43692-9 ISBN 978-1-349-09355-7 (eBook) DOI 10.1007/978-1-349-09355-7

# **Contents**

| Pre | face   |                                                  | ix |

|-----|--------|--------------------------------------------------|----|

| 1   | Introd | luction — Microprocessors in the Computing Scene | 1  |

|     | 1.1    | Microprocessor Systems                           | 1  |

|     | 1.2    | Program Languages and Coding                     | 1  |

|     | 1.3    | Assembly Languages                               | 4  |

|     | 1.4    | High Level Languages                             | 4  |

|     | 1.5    | On-line and Off-line Operation                   | 5  |

|     | 1.6    | Dedicated Microprocessor Systems                 | 6  |

|     | 1.7    | The Elements of a Microprocessor System          | 8  |

|     | 1.8    | The Need for Development Systems                 | 9  |

| 2   | Micro  | processor Registers and their Functions          | 10 |

|     | 2.1    | The Accumulator                                  | 10 |

|     | 2.2    | The Program Counter                              | 11 |

|     | 2.3    | Stack Pointer                                    | 11 |

|     | 2.4    | The Index Register                               | 12 |

|     | 2.5    | Auxiliary Registers                              | 13 |

|     | 2.6    | 6800 Microprocessor Architecture                 | 13 |

|     | 2.7    | Z80 Instruction Set                              | 15 |

|     | 2.8    | 6502 Register Set                                | 17 |

|     | 2.9    | Registers in Interface Packages                  | 18 |

| 3   | Instru | ction Formats and Address Modes                  | 19 |

|     | 3.1    | Instruction Formats                              | 19 |

|     | 3.2    | Addressing Modes                                 | 21 |

|     | 3.3    | Instruction Types                                | 25 |

|     | 3.4    | Data Transfer Instructions                       | 26 |

|     | 3.5    | Arithmetic Operations                            | 28 |

|     | 3.6    | Compare and Test Instructions                    | 30 |

|     | 3.7    | Complement and Negate Instructions               | 31 |

|     | 3.8    | Logical Operations                               | 32 |

|     | 3.9    | Instructions for Incrementing and Decrementing   | 34 |

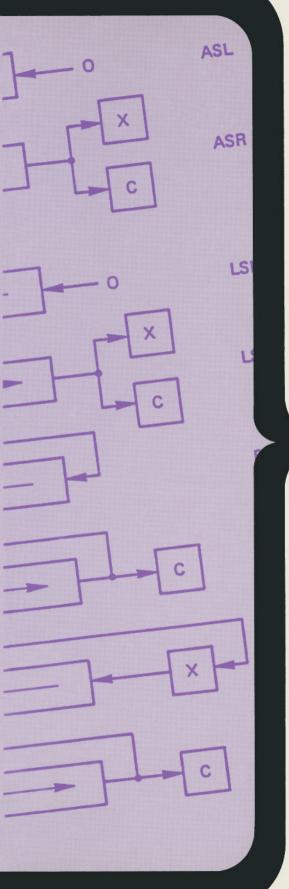

|     | 3.10   | Instructions for Shifting and Rotating           | 35 |

|     | 3.11   | Branch Instructions                              | 37 |

vi Contents

|   | 3.12    | Stack Operations                            | 40 |

|---|---------|---------------------------------------------|----|

|   | 3.13    | Miscellaneous Instructions                  | 41 |

|   |         |                                             |    |

| 4 | Subro   | outines and the Use of the Stack            | 43 |

|   | 4.1     | Subroutines                                 | 43 |

|   | 4.2     | Saving and Passing Variables                | 45 |

|   | 4.3     | Subroutines and Program Subdivision         | 46 |

| 5 | Basic   | Algorithms                                  | 47 |

|   | 5.1     | Addition Programs                           | 47 |

|   | 5.2     | 16-bit Addition                             | 49 |

|   | 5.3     | Subtraction                                 | 50 |

|   | 5.4     | Decimal Arithmetic                          | 51 |

|   | 5.5     | Multiple Addition                           | 52 |

|   | 5.6     | Multiplication                              | 55 |

|   | 5.7     | Division                                    | 59 |

|   | 5.8     | Decimal-to-Binary Conversion                | 60 |

| 6 | Progra  | am Interrupts                               | 62 |

|   | 6.1     | Timing Data Transfers                       | 62 |

|   | 6.2     | Program Interrupts                          | 63 |

|   | 6.3     | M6800 Interrupts                            | 64 |

|   | 6.4     | Interrupt Recognition                       | 65 |

|   | 6.5     | Z80 Interrupts                              | 67 |

|   | 6.6     | Z80 Interrupts Service Routines             | 68 |

|   | 6.7     | 6502 Interrupts                             | 69 |

|   | 6.8     | DMA Transfers                               | 70 |

| 7 | Progra  | amming Input/Output                         | 73 |

|   | 7.1     | Input/Output Packages                       | 73 |

|   | 7.2     | Programming the 6821                        | 74 |

|   | 7.3     | 6502 I/O Packages                           | 77 |

|   | 7.4     | Z80 I/O Package                             | 81 |

|   | 7.5     | Memory-Mapped Input/Output                  | 83 |

|   | 7.6     | Examples of I/O Programming                 | 84 |

| 8 | Aids to | o Program Writing and Testing               | 86 |

|   | 8.1     | The Use of Assemblers                       | 86 |

|   | 8.2     | Example of Assembly                         | 87 |

|   | 8.3     | Cross-assemblers and Editors                | 88 |

|   | 8.4     | The Use of Macros                           | 92 |

|   | 8.5     | Disassemblers                               | 93 |

|   | 8.6     | Linker Programs                             | 93 |

|   | 8.7     | Using Single Shot and Breakpoint Facilities | 93 |

|   |         | - · · · · · · · · · · · · · · · · · · ·     | 75 |

|          |        | Contents                                 | vii |

|----------|--------|------------------------------------------|-----|

| 9        | Single | Chip Microprocessors                     | 95  |

|          | 9.1    | The Single Chip Market                   | 95  |

|          | 9.2    | The 48 Series of Microprocessors         | 95  |

|          | 9.3    | Branch and Control Instructions          | 97  |

|          | 9.4    | Single Chip Versions of Microprocessors  | 98  |

|          | 9.5    | The Z8 Family of Microprocessors         | 98  |

| 10       | 16-bit | Microprocessors                          | 100 |

|          | 10.1   | The Limitations of 8-bit Microprocessors | 100 |

|          | 10.2   | The Intel 8086 and 8088                  | 100 |

|          | 10.3   | Addressing Modes                         | 102 |

|          | 10.4   | Arithmetic Operations                    | 102 |

|          | 10.5   | The Z8000 Family of Microprocessors      | 103 |

|          | 10.6   | Z8000 Arithmetic Instructions            | 105 |

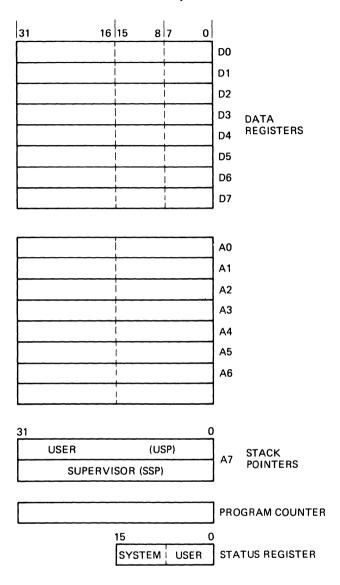

|          | 10.7   | The Motorola 68000 Microprocessor        | 106 |

|          | 10.8   | RISC Systems                             | 108 |

| 11       | The 68 | 8000 Instruction Set                     | 109 |

|          | 11.1   | Introduction                             | 109 |

|          | 11.2   | Data Types                               | 110 |

|          | 11.3   | CPU Registers                            | 111 |

|          | 11.4   | 68000 Instructions                       | 111 |

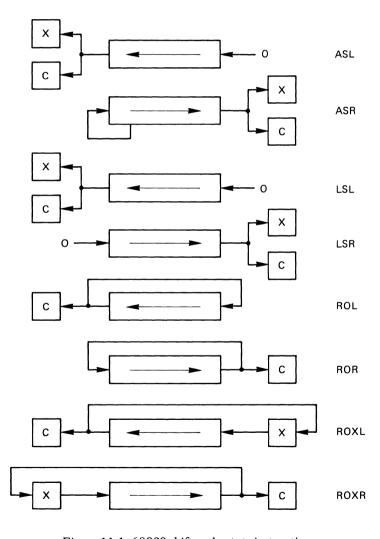

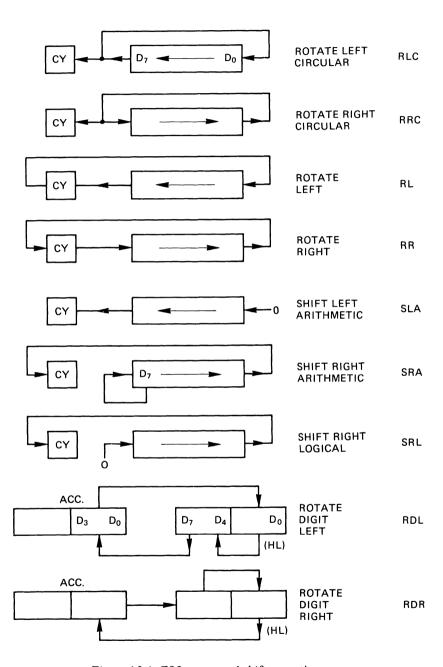

|          | 11.5   | Shift and Rotate Instructions            | 112 |

|          | 11.6   | Branch, Jump and Return Instructions     | 114 |

|          | 11.7   | Addressing Modes                         | 116 |

|          | 11.8   | Data Move Instructions                   | 117 |

|          | 11.9   | Arithmetic Operations                    | 118 |

|          | 11.10  | Logical Operations                       | 120 |

| 12       | Progra | mming the 68 <b>000</b>                  | 122 |

|          | 12.1   | Arithmetic Operations                    | 122 |

|          | 12.2   | BCD Addition                             | 122 |

|          | 12.3   | Block Addition                           | 123 |

|          | 12.4   | Decimal-to-Binary Conversion             | 125 |

|          | 12.5   | Binary-to-Decimal Conversion             | 126 |

|          | 12.6   | Subroutines                              | 127 |

|          | 12.7   | Interrupts                               | 130 |

|          | 12.8   | Software for Program Generation          | 131 |

|          | 12.9   | Features of 68000 Assemblers             | 131 |

|          |        | Examples of Assembler Output             | 133 |

| $Ap_{i}$ | pendix | 1: 6800 Instruction Set                  | 138 |

| Ap       | pendix | 2: Z80 Instruction Set                   | 142 |

| viii | Contents |

|------|----------|

|      |          |

| Appendix 3:  | 6502 Instruction Set  | 150 |

|--------------|-----------------------|-----|

| Appendix 4:  | 68000 Instruction Set | 153 |

| Appendix 5:  | The ASCII Code        | 156 |

| Bibliography |                       | 160 |

| Glossary     |                       | 162 |

| Index        |                       | 164 |

# **Preface**

This book is intended to provide an introduction to machine code and assembly language programming for students and practising engineers who have some acquaintance with microprocessor architecture and operation.

Although several high level languages are now available for microprocessor systems, there is still a need for those concerned with the design, commissioning and repair of these systems to understand assembly language and machine code. Despite the increased programmer productivity which usually accompanies the change from assembly language to a high level language, the resulting program is often 20 per cent longer than it would be if written in assembly language; it will thus be slower to execute. As a consequence, the time-critical sections of a program are often written in assembly language to obtain the most compact code possible.

Also, when testing microprocessor systems any apparatus which records the sequence of instructions executed, for example a logic state analyser, will sense only binary code. This can be disassembled into assembly language to help the programmer to determine what the system is doing, but there are no facilities for converting the program back into a high level language. The same problem arises when modifying programs which are available only in machine code, for example as loaded into a ROM.

In addition to introducing the principles of writing assembly language programs, this book deals with their subsequent conversion into the machine code which the microprocessor can execute.

The first nine chapters are devoted to basic principles and algorithms, with examples which involve the more widely used 8-bit microprocessors. These are now sufficiently powerful to cope with the majority of industrial tasks, but 16-bit devices are becoming cheaper and are thus being used increasingly in the more demanding applications. In consequence, I have given a brief survey of the main 16-bit microprocessors and a more detailed description of the instruction set and assembly language of one of them — the 68000 — in the last three chapters, including some examples of programming and assembly.

I hope that the book will prove of particular help to students who are beginning a microprocessor project and to practising engineers who are encountering microprocessors systems for the first time.

J.C. Cluley

# 1 Introduction—Microprocessors in the Computing Scene

### 1.1 Microprocessor Systems

In increasing order of power and complexity, computer systems are usually divided into microprocessors, minicomputers, and mainframes. The boundaries between the three categories are, however, rather ill-defined and are continually changing as new products come on to the market. The most important feature of a microprocessor is that it is fabricated on a single slice of silicon, by a process which is highly automated and suitable for high volume production. This is essential for low unit cost, since the initial design, layout and mask making is very expensive. Once this cost has been incurred however, if it can be spread over a million or so chips, the cost of each one may be a few pounds or less.

This technology thus enables one to assemble a small working computer for a cost which is 10 to 100 times smaller than that of a minicomputer of equivalent power. In consequence, most microprocessor applications exploit their characteristics of low cost, small size and low power consumption, often using the microprocessor as the controlling element in some instrument, machine tool, process, or domestic product. In these cases the microprocessor must operate without human intervention, and must start working automatically when power is applied to it.

In contrast, most conventional computers require operators to load programs and data, to attend to peripheral devices such as magnetic tape and disc units, line printers, etc. The difference between these two modes of operation implies certain differences between the design of microprocessor systems and that of larger computers, involving both hardware and programs.

# 1.2 Program Languages and Coding

The only coding for data and programs which computers can directly handle consists of groups of binary digits. The number of digits in the group is an important feature of a computer and corresponds to the size of the data highway which in a microprocessor connects the processor, the store, and the interface packages. In the majority of microprocessors the highway is one byte, or 8

binary digits (bits) wide. For simple applications such as hand calculators 4-bit processors suffice and, where a good deal of accurate computation is needed in a short time, 16-bit processors are now available, with 32-bit systems in development. The greater part of this book is devoted to 8-bit microprocessors.

An 8-bit system can represent positive numbers in the range 0 to 255 decimal, or +127 to -128 if negative numbers need to be encoded. This range is inadequate for precise calculations, and two bytes are often taken together to represent positive numbers from 0 to 65 535, or signed numbers between  $+32\,767$  and  $-32\,768$ . This range suffices for many problems concerned with measurement and control, since it permits much greater precision in representing variables than the vast majority of transducers used to measure pressure, temperature, torque, etc. can attain.

Negative numbers are usually represented in what is called the 2's complement notation. In this, each bit apart from the most significant (left-hand) bit represents a positive number, and the most significant (MS) bit represents a negative number. For an 8-bit system the bit values are shown in the table below.

| Code               |              |            |            | Bit N      | Vumbe | r        |          |          |               |

|--------------------|--------------|------------|------------|------------|-------|----------|----------|----------|---------------|

|                    | 7            | 6          | 5          | 4          | 3     | 2        | 1        | 0        |               |

| Unsigned<br>Signed | +128<br>-128 | +64<br>+64 | +32<br>+32 | +16<br>+16 | +8    | +4<br>+4 | +2<br>+2 | +1<br>+1 | Bit<br>values |

Thus +20 in decimal is represented by 00010100, and -100 by 10011100. In all cases the MS digit is 0 for a positive number and 1 for a negative number, and for this reason is often called the *sign digit*.

Program information, like data, is fed into microprocessors in groups of binary digits. Because instructions vary in their complexity, and thus in the amount of information they need to convey, they vary in size. Thus, for 8-bit systems, instructions may be from one to four bytes long, but always a whole number of bytes.

Although the microprocessor can accept only binary coded information, this representation is extremely awkward for writing down and checking programs. For convenience we need a more compact notation; this is usually obtained by using one symbol to denote four bits so that each byte comprises only two symbols. Consequently each symbol must encompass 16 (or 2<sup>4</sup>) different values. These are obtained by using the 10 numerals and the first 6 letters of the alphabet. We are thus encoding data and instructions in a numbering system with the base 16. This is called *hexadecimal* notation, and is used in all manufacturers' literature to specify instructions and addresses.

Many devices which provide a conventional decimal read out, such as digital voltmeters and frequency meters, provide electrical signals which can be connec-

ted to a microprocessor. These usually give a 4-bit version of each decimal digit of the display. Thus a display of 345 would give an electrical output of 0011 0100 0101. This is called binary coded decimal (BCD) format and where only simple arithmetic operations on the data are required it may be convenient to keep the data in this form. Many microprocessors have instructions to add BCD numbers, so that simple calculations are possible with some sacrifice in speed. However, this procedure saves the time that would otherwise be devoted to converting from BCD to binary and back to BCD if a decimal output is required. The following table shows the first 20 numbers encoded in different ways.

| Decimal | Binary | Hexadecimal | BCD       |

|---------|--------|-------------|-----------|

| 0       | 00000  | 00          | 0000 0000 |

| 1       | 00001  | 01          | 0000 0001 |

| 2       | 00010  | 02          | 0000 0010 |

| 3       | 00011  | 03          | 0000 0011 |

| 4       | 00100  | 04          | 0000 0100 |

| 5       | 00101  | 05          | 0000 0101 |

| 6       | 00110  | 06          | 0000 0110 |

| 7       | 00111  | 07          | 0000 0111 |

| 8       | 01000  | 08          | 0000 1000 |

| 9       | 01001  | 09          | 0000 1001 |

| 10      | 01010  | 0 <b>A</b>  | 0001 0000 |

| 11      | 01011  | 0 <b>B</b>  | 0001 0001 |

| 12      | 01100  | OC          | 0001 0010 |

| 13      | 01101  | 0D          | 0001 0011 |

| 14      | 01110  | 0E          | 0001 0100 |

| 15      | 01111  | 0F          | 0001 0101 |

| 16      | 10000  | 10          | 0001 0110 |

| 17      | 10001  | 11          | 0001 0111 |

| 18      | 10010  | 12          | 0001 1000 |

| 19      | 10011  | 13          | 0001 1001 |

| 20      | 10100  | 14          | 0010 0000 |

For completeness, the code used to communicate with printers and terminals such as teleprinters and visual display units should be mentioned. This is usually called ASCII (American Standard Code for Information Interchange) although it has now achieved international acceptance as ISO-7 code. This is a 7-bit code which can be sent in either serial or parallel mode. It is often transmitted as an 8-bit byte, where the 8th bit is available for error detection when sending over links such as telephone lines which are liable to noise and interference. A list of ASCII codes is given in appendix 5.

# 1.3 Assembly Languages

Although programs can be written more compactly by using hexadecimal notation rather than binary, a list of instructions such as

21 E0 0C 7E 23

does not immediately show what operations are required. In order to help programmers, manufacturers usually publish a list of mnemonics for the instructions which indicate their function. Typical of these are

LDA Load Accumulator

STA Store Accumulator

INC Increment

DEC Decrement

ADD Add

SUB Subtract

ADC Add with Carry

With a little practice, this form of coding enables one to read programs as easily as if they were written in BASIC. The instructions listed in hexadecimal notation at the beginning of the paragraph would be written as

LD HL OCEO

LD A (HL)

Load Accumulator from above address

INC HL

Increment Address

This form of coding is called Assembly Language and is clearly easier to read than the hexadecimal code form, called Machine Code. Programs written in assembly language can be converted into machine code by using programs called Assemblers. More details of these and their use are given in chapter 10.

### 1.4 High Level Languages

Where complex problems are involved it is convenient if the language used to write the program is designed to suit the problem, rather than arising from the hardware design of the processor, as assembly language is. A language of this sort is called a *High Level Language*. It reduces the size of programs drastically, since each statement, occupying one line, may translate into many machine code

instructions. An assembly language instruction on the other hand normally translates into one machine code instruction. Most microcomputers have facilities for using the language BASIC, which enables a form of algebraic expression to be used. Thus one may specify the value of a variable Z in terms of other quantities X and Y by an expression such as

$$Z = 45.78*SIN(X) + Y^{4}$$

In conventional notation this would be written as

$$Z = 45.78 \sin(X) + Y^4$$

the \* denoting multiplication, and the  $\uparrow$  exponentiation  $(Y \uparrow 4 = Y^4)$ .

In order to effect this calculation in assembly language one would need to store the coefficients of the power series which evaluates the sin function and include program segments to generate exponential functions. BASIC includes commands to generate square roots, random numbers, logarithms, etc. If these facilities can be used, they avoid the need for much assembly language programming, but the disadvantage is that programs written in BASIC typically take 20 to 30 times longer to run than equivalent programs in assembly language. In some critical control applications, this waste of time cannot be tolerated and assembly language must be used. More often, where the program spends much of its time executing a few subroutines, these can be written in assembly language. The overall program execution time is then much reduced. Many versions of BASIC allow machine code subroutines to be called from programs written in BASIC.

BASIC is slow in execution since it is normally stored in its source form and each statement is converted into machine code immediately before execution, by a program called an *interpreter*. Earlier high level languages such as Fortran which were converted into machine code in a separate operation prior to execution ran at speeds much closer to that of assembly language programs. They were somewhat slower since the machine code produced by the conversion program or compiler was not as compact as that produced by writing directly in assembly language.

BASIC in its original form was inconvenient for many control applications since it made no provision for setting, clearing and testing the individual bits in a byte, tasks often needed in such programs. Later high level languages such as C include this provision and most of them enable machine code program segments to be included in the main high level language program to perform bit handling.

### 1.5 On-line and Off-line Operation

When considering the way in which a microprocessor interacts with its environment and with the devices attached to it, we can distinguish two possible arrange-

ments, called *On-line* and *Off-line*. In the off-line mode the microprocessor is performing some task such as preparing a payroll or calculating the stresses in a structure. Once the program and data have been loaded, the program execution proceeds without further intervention until the results are printed out. There is no direct relation between the time taken for the calculation and any time factors in the problem. In the payroll example, the interval between runs is clearly an upper limit to the running time of an acceptable program, so that a program which took a week to run would not be much use! However, it would not affect the program's utility much if the inclusion of extra features increased the running time from, say, 20 minutes to 25 minutes.

With on-line working the microprocessor is part of a larger system and provides the data handling and computation needed to ensure satisfactory operation. The microprocessor is continuously receiving information from the system and is required to provide outputs which may, for example, regulate the system according to some criterion laid down by the designer. In such an arrangement the microprocessor is required to execute a control program each time a new set of inputs appears, and so to determine what outputs to the system are needed. The running time of the program must be small, otherwise the regulating signals will be fed in too late and the system will become unstable. The control program must contain a segment which scans all of the inputs at regular intervals so that any input changes are rapidly detected and acted upon.

The time available for the program is thus directly linked to the time factors in the system response, or in simpler terms to the delay between the arrival of a disturbance on one of the system inputs and the resulting change in the system output. This limitation may be of little practical significance in systems such as large boilers where conditions can only change relatively slowly, but it becomes a critical factor in the design of very fast systems such as those used for missile guidance.

Other on-line systems which are not involved in regulation or control may impose less stringent conditions on the program. For example, point-of-sale terminals need only keep pace with the relatively slow rate at which the operator can key in details of the transaction.

# 1.6 Dedicated Microprocessor Systems

Most on-line microprocessors form part of a larger system for which they provide the computing and control function. In consequence, they are required to execute only the program needed for this function, and to do so automatically without any human intervention. For example, the microprocessor which is built into a washing machine must begin its control program as soon as the power supply is switched on. This requirement imposes some constraints on the hardware and technology of the microprocessor system and to a lesser extent on the program it executes. The major feature is that the program must be held in

the system in an incorruptible form which cannot be overwritten by some unexpected input signal. Also the program must be available the moment power is supplied to the system.

These demands are satisfied by using Read Only Memory (ROM) to store the program. The program is either built into the store chip during its fabrication, or loaded in by the system manufacturer, and once the chip is connected into the microprocessor unit its contents cannot be changed. The microprocessor itself has an input labelled RESET or RESTART which must be energised for a few milliseconds after power has been applied to the system. This sets a fixed address into the program counter (a register which holds the address of the next instruction to be executed) and the microprocessor either starts to execute a program beginning at this address, or it reads the contents of this address and the next byte and uses them as a 16-bit address where it will find the starting address of the program. In either case the fixed address which is determined by the manufacturer of the microprocessor must refer to some location in a ROM package. Since this package normally also holds the program, it is convenient to locate the program ROM in the same store area as that chosen for the fixed address. There is no uniformity about this; for example, the 8085 microprocessor always clears the program counter on receipt of a Reset signal, so that the program must always start from location 0000. On the other hand the 6800 always reads the contents of locations FFFE and FFFF to look up the starting address of the program. In this case it is convenient to locate the program ROM at the top of the address space since there must be ROM for the microprocessor to read at all locations from FFF8 to FFFF.

For fully automatic operation, it is essential that the RESET pulse should be generated immediately the power is applied. This can easily be arranged by using a trigger circuit initiated by the rise in voltage of the power supply line; in some microprocessors the trigger circuit may be on the microprocessor chip itself, and the only external components needed are a resistor and a capacitor. The RESET pulse is often extended to the peripheral packages of the system so that registers in these packages can be cleared when power is applied. This ensures that all of these registers will be in a known state when program execution starts.

Some microprocessor systems used in commerce and industry could be described as partly dedicated. They contain a program in ROM variously called a Monitor, Executive or Operating System which allows the operator to load the program and data for some particular task such as payroll, and then run the program. When this has finished, the next program and its data may be loaded, for example to print invoices. The program and data are normally held on floppy discs which the operator must select and then load into the disc drive. In this kind of system there must be sufficient writable store to hold the various programs one at a time, together with their data. Some microprocessors which are concerned with only a few programs may avoid the need for program storage on disc by holding the program in ROM. If there are several ROMs they can all occupy the same address space and be selected individually when required via

the operating system. With this arrangement the system needs only sufficient Random Address Memory (RAM) or writable store to hold the data and the complement of ROM and RAM is much nearer to that of a fully dedicated microprocessor.

# 1.7 The Elements of a Microprocessor System

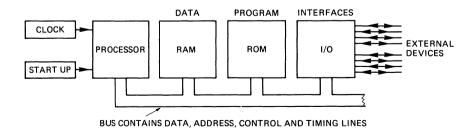

A block diagram of a typical microprocessor system is shown in figure 1.1. The microprocessor chip itself requires a number of other packages to be added to it before it can perform any useful work. In the system shown the processor has a start-up circuit attached which provides the RESET pulse needed to start the program execution. The clock pulse generator provides a regular train of pulses which synchronise the actions of the various packages connected together. Both of these items are entirely hardware-controlled and not affected by the program. This is stored in the ROM package which is connected in a party-line manner to the microprocessor, the RAM and the input/output packages by means of a Bus or highway.

The Bus may contain 8 data lines, 16 address lines, and some 8 to 12 lines carrying control and timing information. The programmer has access to *Registers* which can store one or more bytes and form part of the store and input/output packages. The function of the registers in typical microprocessors and associated packages is discussed in more detail in chapter 2.

Data transfers from the microprocessor to the other packages can be used either to store data in the RAM, send a command signal to control a peripheral device, or send data to it. In the other direction, they can be used to read from the stores, examine the state of peripheral devices, or read data from them.

The diagram is simplified in that more than one package of ROM, RAM or input/output may be needed to satisfy the system requirements. Store packages are typically made in a range of sizes, accommodating for example 1K, 2K, 4K, 8K and 16K bytes. By using a suitable combination of these a program of any size can be stored with little unused space.

Figure 1.1 Block diagram of typical microprocessor system.

Although few details of the circuit are of direct concern to the programmer, he must know exactly what is connected to each of the input and output lines and what function they perform. Information is exchanged between the microprocessor and the other packages of the system in units of one byte although only one bit may need to be changed to exercise some particular action. Thus the programmer must have instructions available to test, set and clear individual bits of a data byte. Some microprocessors which are intended specifically for control applications have instructions to perform these actions directly; others require several instructions for the same action.

# 1.8 The Need for Development Systems

Although the diagram shown in section 1.7 is typical of many working systems, it is not suitable for developing and testing programs prior to committing them to ROM. A high volume product will normally use a masked ROM in which the program is built into the chip in the final metallising process. This connects up all of the cells in the store and determines whether their output is 1 or 0, and requires a special mask containing the program information. The cost of a mask is typically several thousand pounds, so that it is important to ensure that the program contains no faults before ordering the mask. As originally written it is almost certain that there will be some errors, so that an essential feature of a system which is used for development is the ability to load programs, run them, and quickly correct any errors found. The program is held in RAM and when it appears correct a copy must be taken to make the mask, or to load a programmable ROM (PROM).

A range of systems has been offered for development, ranging from simple arrangements which provide a hexadecimal keyboard for data input and a set of 7 segment lamps for the display to more complex systems which include an assembler, a printer or VDU for the display, and provision for automatically loading the program into a PROM. Such systems often include a floppy disc store for programs under development and perhaps a serial data channel to feed in programs which have been assembled in a larger computer, or to 'down-load' an assembled program into a microprocessor in order to test it.

In order to test the program and locate faults in it, a monitor program is generally used. This will allow user programs to be run an instruction at a time, with provision for examining the processor registers after each step, or running the program at full speed until a 'breakpoint' is reached and then single stepping. It will also enable any program instruction to be changed when a fault is found. More detailed consideration of the use of these facilities is given in chapter 10.

# 2 Microprocessor Registers and their Functions

#### 2.1 The Accumulator

Most of the program activity in microprocessor systems is concerned with moving information into and out of various registers. These are high-speed storage elements inside the central processor. Consequently, before discussing the action of different instructions it is necessary to understand the way in which microprocessor registers are used and their particular functions. Not all microprocessors have the same set of registers, but all of them have one or more *Accumulators*.

The Accumulator is the main register concerned with arithmetic and logical operations because the result of nearly all such actions is loaded into the accumulator. Also input and output transfers normally copy the contents of the accumulator onto the bus and thence into the data register of some peripheral package, or copy the contents of such a register into the accumulator. In the latter case the previous contents of the accumulator would be destroyed.

In 8-bit microprocessors the accumulator is an 8-bit register, but some devices allow two registers to be used together to store a 16-bit number. For example all members of the 6800 family have two accumulators, and almost all instructions involving accumulators have two versions, one using accumulator A and the other accumulator B. One member of the family, the 6809, has a multiply instruction in which the two 8-bit numbers in the two accumulators are multiplied together and the product is left in both accumulators as a 16-bit number, the most significant byte in accumulator A, and the least significant byte in accumulator B.

Associated with the accumulator is the flag register, also called the condition code register or the processor status register. This comprises a number of status bits which are set after arithmetic operations if certain conditions are satisfied and cleared if not. The usual conditions are

- 1. Zero result

- 2. Negative result

- 3. Overflow

- 4. Carry

- 5. Half-carry

Overflow denotes a carry from bit 6 to bit 7 of the result, meaning that two positive quantities have been added together to form a sum too large for the accumulator to handle, so that it represents a negative number. Alternatively, two negative numbers have been added to give a positive sum. The carry bit is in effect an extra 9th bit which holds a carry from the 8th bit of the accumulator. It is also used as part of the circulation path in many Rotate instructions. The half-carry bit is set when a carry from bit 3 to bit 4 occurs. This information is needed for performing arithmetic on BCD numbers. Other bits may indicate that the interrupt line is disabled, or may denote the parity of the accumulator contents.

# 2.2 The Program Counter

The Program Counter (PC) is usually a 16-bit register which is used to keep track of the program execution. It always contains the address of the next instruction byte required by the processor, and so its contents are used to fetch each instruction in turn, byte by byte. Its initial contents are either fixed by the manufacturer, or are stored at two addresses fixed by the manufacturer. In the latter case the microprocessor is built so that on receipt of the Reset pulse it uses the contents of these locations as the starting address of the program.

The programmer can change the contents of the PC by means of a branch or jump instruction, or by a return from subroutine or return from interrupt, but not by direct arithmetic operations. When jumping to a subroutine, the contents of the PC (the return link) must be saved and then restored at the end of the subroutine, to allow the processor to continue execution of the main program. The two actions are carried out automatically as part of the Jump to Subroutine and the Return from Subroutine instructions, and require no further action by the programmer.

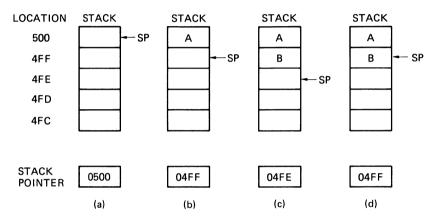

#### 2.3 Stack Pointer

The stack pointer is another 16-bit register used to control access to the *Stack*. This is an area of RAM which is used to store the return link for subroutines and interrupt service programs, and may also be used by the programmer to store variables temporarily, or to transfer them between the main program and a subroutine. The stack is organised in a different way from normal RAM in that no addresses are specified when putting a byte into store or removing it from store. The only access is to the top location of the stack; as this fills up the address of the next free location is held by a 16-bit register called the *Stack Pointer*. By convention the stack starts at the highest address of the block of RAM allocated to it. Each time an item is loaded onto the stack the stack pointer is afterwards decremented (1 is subtracted from it). Conversely, each time an

item is removed from the stack, the stack pointer is incremented (1 is added to it) before using it to point to the item.

Figure 2.1 shows the changes to the stack as two items are added to it and one is removed. The stack is initially empty and its top address is 500 (hex). The operation of putting an item onto the stack is called *Push* and that of removing it is called *Pull* or *Pop*. This type of store is also called LIFO (Last In First Out), and it is very convenient for storing subroutine return links. If subroutines are *Nested*, that is one subroutine can call another subroutine, the return links are automatically put onto the stack so that they are in the correct order to pull from the stack when returning to the main program.

Figure 2.1 Contents of stack and stack pointer as stack is used:

(a) empty; (b) byte A loaded; (c) byte B loaded; (d) byte B pulled off stack.

Only a limited number of operations can normally be performed on the contents of the stack pointer such as loading or storing, and incrementing or decrementing. Some microprocessors, however, allow them to be used in 16-bit addition and subtraction. In all cases the stack pointer must be initially loaded with the address of the top of the stack before any stack operations can be performed satisfactorily.

# 2.4 The Index Register

The index register (IR) is a 16-bit register which is intended to help addressing sequentially the items in a block of data. For example, if we require to add together all of the items, we can use the same add instruction repeatedly by means of indexed addressing. The format of the instruction is

This means 'Add to accumulator using indexed addressing with an offset of 20'. The address of the item added is obtained by adding together the contents of the IR and the offset 20 (normally taken as hexadecimal). The same instruction will handle the next item in the list if the contents of the IR are first incremented. The program uses a small loop for this action and has the advantage that its size is the same however many items there are in the list. Examples of the use of the IR for this purpose are given in chapter 7.

The index register may also be used for looking up a particular item in a table. For example, if we require the 6th item we can load the address of the first item into the IR. We can then either add 6 to the IR or increment it 6 times. Most microprocessors provide instructions for incrementing and decrementing the IR, but its contents need to be moved to the store or to another register pair in order to add to them.

Where a block of data needs moving from one store area to another a single IR is awkward to use, and the program can be shorter and run more quickly if two IRs are available. One can index the addresses of the originating block, and the other the addresses of the block into which the data is moved. For this reason some microprocessors are provided with two IRs.

The IR is also used as a 16-bit register for counting or timing where indexed addressing is not needed.

## 2.5 Auxiliary Registers

Some microprocessors, for example the Z80, 8080 and 8085, which have a single accumulator include a number of general-purpose registers which can be used to hold data being used in a calculation. Their contents can be incremented, decremented, added to, or subtracted from the contents of the accumulator. Data held in them need not be moved into the store and returned when needed, so saving time in running the program. Pairs of them can also be used to hold 16-bit numbers or 16-bit addresses.

The Z80 has some registers duplicated to allow rapid response to a program interrupt. The instructions for using these and their advantages are discussed in chapter 8.

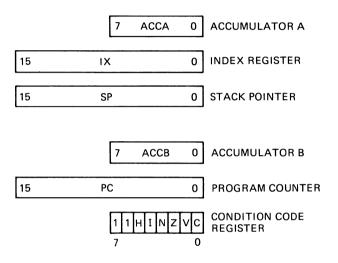

# 2.6 6800 Microprocessor Architecture

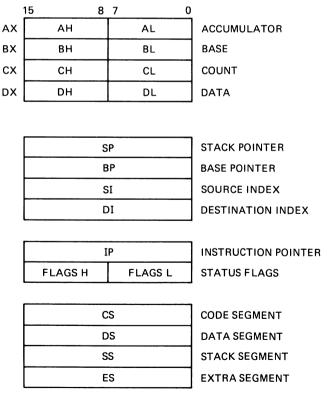

Having explained the function of the various processor registers in general terms, we now turn to the architecture of typical microprocessors as they concern the programmer, starting with the 6800. This was designed by Motorola, but has since been second sourced by a number of other manufacturers. Its instruction set and design bear a marked resemblance to those of the PDP-11 minicomputer, a 16-bit family of minicomputers made by Digital Equipment Corporation. The

register set is shown in figure 2.2. Its particular feature is that two accumulators are provided, so simplifying many arithmetic operations. Almost all instructions have two versions, one using accumulator A and the other accumulator B. The only exceptions are DAA which adjusts an Add operation to cope with BCD data and is available only with accumulator A, and ABA which adds together the contents of the two accumulators, but leaves the result in accumulator A.

Figure 2.2 6800 microprocessor registers.

There are no auxiliary 8-bit registers, but the IR can be used as a counter or register if not needed for indexed addressing. Like the PDP-11, the 6800 is a universal bus device in which all types of storage package and all input/output registers share a common address space of 64K bytes, using 16 address lines. This has the advantage that the full set of arithmetic and logical instructions can be performed on the registers of the input/output packages. Earlier microprocessors, such as the 8080, had only two input/output instructions; one copied the contents of the accumulator out to the input/output package, and the other sent data in the reverse direction.

The flags are collected in the condition code register and their significance is shown in the table below. The two most significant bits are not connected and so always read as 1.

| Bit Number | Condition  |

|------------|------------|

| 0          | Carry      |

| 1          | Overflow   |

| 2          | Zero       |

| 3          | Negative   |

| 4          | Interrupt  |

| 5          | Half-Carry |

### 2.7 Z80 Instruction Set

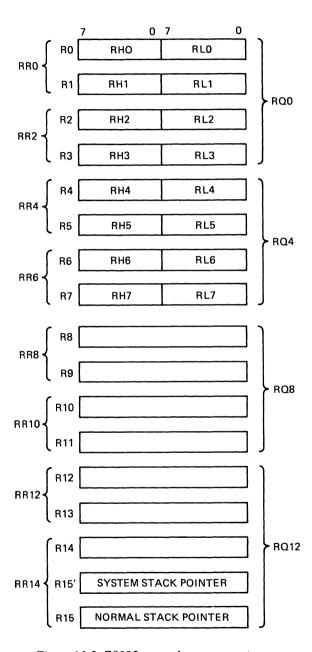

The Z80 was designed by Zilog Inc. to be upwards compatible with the 8080, so that its register set resembles that of the earlier machine. Extra registers are also included to provide quicker block moving operations, more comprehensive interrupt handling, and simple refreshing of dynamic RAMs. It is now made by several other manufacturers.

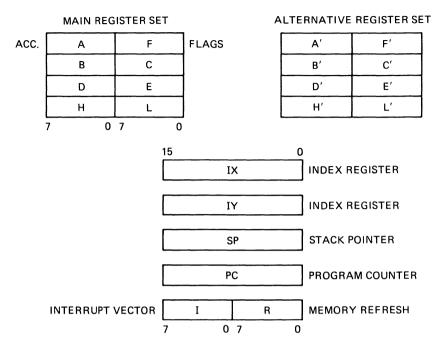

Only one accumulator (A) is included but four general-purpose single byte registers -B, C, D, and E — allow a number of variables to be held in the processor. This saves time when they are required for computation since they can be loaded into the accumulator in four clock cycles compared with the seven cycles needed to fetch data from the external store. Two other registers (H and L) hold the address of the location in the store which is to be accessed, and if not needed for this can be used as general-purpose registers. The complete set is shown in figure 2.3.

In order to speed up the handling of interrupts, duplicate registers A' to L' are provided so that the state of the processor need not be saved in external storage during the interrupt handling routine.

Pairs of registers (BC, DE, and HL) can be used together to hold 16-bit numbers, with limited facilities for arithmetic operations.

Block data move operations are aided by having two index registers, one of which can be used to select the source and the other the destination of the move. The I register can be loaded by program and holds the most significant byte of the vector address when Interrupt mode 2 is enabled. For completeness the Refresh register is shown, although this cannot be accessed by the programmer. It is used to generate a refresh address for dynamic RAM which is output on the address lines when these are not otherwise needed by the processor. Its contents are incremented after each transfer by the processor and no program action is needed.

Figure 2.3 Z80 microprocessor registers.

The accumulator flags are collected in a Flag register and are located as follows.

| Bit Number | Condition       |  |  |

|------------|-----------------|--|--|

| 0          | Carry           |  |  |

| 1          | Subtract        |  |  |

| 2          | Parity/Overflow |  |  |

| 4          | Half-Carry      |  |  |

| 6          | Zero            |  |  |

| 7          | Sign            |  |  |

The flag meanings are slightly different from those of the 6800. Bit 1 is set if the last operation was a subtract, otherwise it is cleared. Bit 2 has two functions; it is set if the result of the last arithmetic operation was an overflow, otherwise it indicates even parity of a logical operation. It is thus set for even parity (an even number of ones in the byte), and cleared for odd parity.

The program counter and the stack pointer operate in exactly the same way as the corresponding registers in the 6800.

## 2.8 6502 Register Set

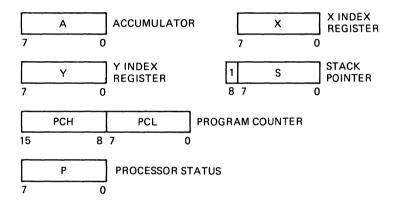

The 6502 was designed by Rockwell International Corp. and bears a family resemblance to the 6800. It is now made by several other manufacturers. It has only one accumulator, however, and two index registers, but these store only 8 bits. The program counter stores 16 bits, as usual, but the stack pointer holds only one byte. It has a 9th bit hardwired as a 1 so that it can store addresses in the range 100 to 1FF (hex). Figure 2.4 shows the set of 6502 registers.

Figure 2.4 6502 microprocessor registers.

Although there are two index registers each one holds only 8 bits, thus restricting the IR. However, any store location can be accessed because the instruction for indexed addressing contains three bytes. The first is the operation code, and the second and third contain a 16-bit address which is added to the IR to obtain the effective address. This is different from the scheme used in other chips in which the IR holds 16 bits and the displacement coded in the instruction holds only 8 bits. The two IRs (X and Y) can also be used for indirect addressing; that means that the effective address calculated from the instruction and the IR contains not the operand but the address of the operand. The 6502 has thus a greater variety of addressing modes than the two previous microprocessors. These are discussed in greater detail in the next chapter.

The flags are collected in a processor status register and have the significance as shown in the table below.

| Bit Number | Condition         |  |  |

|------------|-------------------|--|--|

| 0          | Carry             |  |  |

| 1          | Zero              |  |  |

| 2          | Interrupt Disable |  |  |

| 3          | Decimal Mode      |  |  |

| 4          | Break Bit         |  |  |

| 6          | Overflow          |  |  |

| 7          | Negative          |  |  |

Bit 2 is set when the IRQ interrupt line is disabled, and is under the programmer's control. Bit 3 is set when arithmetic operations are to be performed in BCD format. Bit 4 is set when the program is interrupted by a Break instruction. The other bits denote conditions similar to those in other microprocessors.

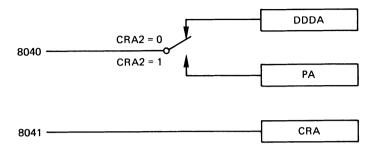

#### 2.9 **Registers in Interface Packages**

In addition to the registers within the processor the programmer needs to write to and from registers in the various packages which are attached to the bus. These are used to control external devices and the registers have broadly three functions: to handle data, to read information about the status of the device, and to write commands to it. In addition the interface package can be configured in a number of ways by program, so that before passing data control registers must be loaded to determine the exact function of the package. For example, in a parallel input/output package we may need to specify

- (a) Whether control signals can create program interrupts.

- (b) Whether each data line is an input or an output.

- (c) Whether the control line sets a flag on the rising edge or the falling edge of its input signal.

- (d) Whether one control line is to be an input or an output.

In some cases only a few control lines are needed and a single-byte register can hold both status (read) and control (write) bits. When performing a read operation to determine, for example, whether a flag is set it will then be necessary to mask out the other status bits and the control bits so that the flag information only is presented. More detailed discussion of the programming of input/output operations is given in chapter 9.

# 3 Instruction Formats and Address Modes

#### 3.1 Instruction Formats

All microprocessor instructions comprise a whole number of bytes; the first always contains the operation code (often abbreviated to op. code). If the instruction does not need to specify an operand or its address, this single byte suffices. Some examples are given below in the customary hexadecimal coding.

| Microprocessor | Mnemonic | Code       | Action              |

|----------------|----------|------------|---------------------|

| 6800           | CLRA     | 4F         | Clear Acc. A        |

| 6800           | COMA     | 43         | Complement Acc. A   |

| 6800           | DECA     | 4 <b>A</b> | Decrement Acc. A    |

| 6800           | INCA     | 4C         | Increment Acc. A    |

| 6800           | INX      | 08         | Increment IR        |

| <b>Z</b> 80    | LD A, B  | 78         | Copy B Reg. to Acc. |

| <b>Z</b> 80    | LDB, A   | 47         | Copy Acc. to B      |

| <b>Z</b> 80    | INC A    | 3C         | Increment Acc.      |

| <b>Z</b> 80    | DEC A    | 3D         | Decrement Acc.      |

| <b>Z</b> 80    | ADD A,B  | 80         | Add B to Acc.       |

| 6502           | TAX      | AA         | Copy Acc. to X Reg. |

| 6502           | INX      | E8         | Increment X Reg.    |

| 6502           | DEX      | CA         | Decrement X Reg.    |

| 6502           | ROL A    | 2 <b>A</b> | Rotate Acc. left    |

Two-byte instructions provide one byte for the op. code and one for the address of the operand, or the operand itself. Clearly, with this restriction, only part of the store can be accessed, usually Page 0 (the first 256 bytes), and if the operand is held in the second byte the instruction can load only an 8-bit register. The operand, like the op. code, is normally given in hexadecimal code, but some assemblers allow decimal or binary numbers if these are preceded by a marker symbol.

| Typical | two-byte | instructions | are |

|---------|----------|--------------|-----|

|---------|----------|--------------|-----|

| Microprocessor | Mnemonic | Op. Code   | Action             |

|----------------|----------|------------|--------------------|

| 6800           | ADDA # n | 8B         | Add n to Acc. A    |

| 6800           | ADDA n   | 9 <b>B</b> | Add (n) to A       |

| 6800           | ANDA # n | 84         | AND A with n       |

| 6800           | LDAA # n | 86         | Load n into A      |

| 6800           | LDAA n   | 96         | Load (n) into A    |

| <b>Z</b> 80    | LDB, n   | 06         | Load n into B      |

| Z80            | ADD A, n | C6         | Add n to A         |

| <b>Z</b> 80    | AND n    | E6         | AND A with n       |

| <b>Z</b> 80    | OR n     | F6         | OR A with n        |

| 6502           | LDA # n  | <b>A</b> 9 | Load n into A      |

| 6502           | LDA n    | <b>A</b> 5 | Load (n) into A    |

| 6502           | CMP # n  | <b>C</b> 9 | Compare n with A   |

| 6502           | LDX # n  | <b>A</b> 2 | Load n into Reg. X |

Here, in the right-hand column n denotes an operand, (n) denotes the contents of location n.

The second byte of the instructions for the 6800 and the 6502 can be either the operand or its address. In order to distinguish between these two, a hash sign (#) precedes an operand. Thus

#### LDA #10

means 'Load the Accumulator with the numerical value 10', whereas

#### LDA 10

means 'Load the Accumulator with the contents of location 10'. The numbers are normally given in hexadecimal coding. The Z80 has no instructions which embody a single-byte address, so all the examples above refer to the operand itself and there is no need for the hash sign.

Branch instructions are normally two-byte instructions; the second byte contains the offset or displacement. This is the number which must be added to the program counter if the branch condition is satisfied. Since the number is involved in the calculation of the effective address and is not an operand, the hash sign is not needed.

Three-byte instructions normally involve either a full 16-bit address or a 16-bit operand as the last two bytes. They are thus required when loading 16-bit registers or pairs of 8-bit registers, as shown in the examples below.

| Microprocessor | Mnemonic     | Code            | Action                                   |

|----------------|--------------|-----------------|------------------------------------------|

| 6800           | ADDA 2000    | BB2000          | Add to A contents of Location 2000       |

| 6800           | DEC 3000     | 7A3000          | Decrement contents of Location 3000      |

| 6800           | LDX 4000     | CE4000          | Load 4000 into IR                        |

| <b>Z</b> 80    | LD SP, 5000  | 310050          | Load 5000 into SP                        |

| <b>Z</b> 80    | LD HL, 6000  | 210060          | Load 6000 into register pair HL          |

| <b>Z</b> 80    | LD A, (7000) | 3 <b>A</b> 0070 | Load contents of<br>Location 7000 into A |

| 6502           | LDA 1000     | AD0010          | Load contents of<br>Location 1000 into A |

| 6502           | LDX 2000     | AE0020          | Load contents of Loc. 2000 into X reg.   |

An examination of the instruction codes shows one of the difficulties in machine code programming — the lack of a uniform method of specifying 16-bit numbers. In the 6800 the high-order byte is coded first, whereas in the Z80 and the 6502 the low-order byte comes first. Thus in the 6502 the op. code for Load Accumulator with an immediate operand is AD, and to load the operand 1234 the code required is

#### AD 34 12

Of the three microprocessors discussed here only the Z80 has four-byte instructions. They are used for the bit test, set and clear instructions where a particular bit of a particular register must be specified, and also the operation to be performed on it. Also operations such as loading an index register use a two-byte op. code. For example, to load index register IX with the operand 1234 would require the four bytes

#### FD 21 34 12

# 3.2 Addressing Modes

Microprocessor instructions allow either one or two bytes for the address. The number concerned may be interpreted in a variety of ways, called address modes,

each involving a different method of calculating the Effective Address, or the location which holds the actual operand.

The following list includes those generally found in microprocessor instruction sets.

- (a) Immediate Address. In this case the number stored in the instruction is the operand itself, sometimes called a 'Literal'. It consists of one byte for an 8-bit operation, and two bytes for a 16-bit operation.

- (b) Direct Address. This means that the one or two bytes after the op. code contain the actual address of the operand. It is also called Absolute Addressing. Some microprocessors have special instructions for accessing the bottom 256 bytes of the store; this needs only one address byte and so the instruction takes up less storage space than one with a 16-bit address and also executes in less time. It, of course, requires that this area of the store should contain RAM used to hold variables and temporary data. In the 6800 this is called Direct Addressing and in the 6502 Page Zero Addressing. It is not provided in the Z80 since the bottom of the store is needed for program.

- (c) Indexed Address. This is generally a two-byte instruction in which the second byte holds an offset which is added to the contents of the index register to generate the effective address. The offset is normally treated as an unsigned number. An example in 6800 code is

### LDAA 50, X

This encodes to A6 50. It will load accumulator A with the contents of location 1050 if the IR contains 1000. The IR contents are sometimes called the Base Address. The main purpose of indexed addressing is to allow lists and blocks of data to be handled easily. For example, the same instruction can be used repeatedly to access successive items of data by incrementing the IR before each operation. Some examples of this are given in chapter 7.

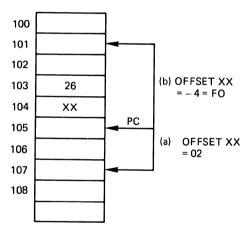

(d) Relative Address. In this mode the second byte of the instruction contains a number (often called the offset) in two's complement notation which has to be added to the contents of the PC to obtain the effective address. The address is thus computed relative to the PC. A one-byte number limits the offset to between +127 and -128. Note that the offset has to be added after the instruction has been fetched, and is thus added to the address of the first byte of the following instruction.

Relative addressing is used mainly for branch instructions; for example, the op. code for 'Branch if not equal to zero' (BNE) is 26. For the program segment shown in figure 3.1 a branch to location 107 needs the PC to be advanced two bytes, so the offset XX must be 02. For a branch backwards to location 101, the PC must be reduced by 4. The offset is thus -04, or in two's complement notation FC. This can be derived by subtracting 4 from

100 in hexadecimal notation, or by converting 04 into binary notation and calculating the two's complement. In either case one can check that the offset is correct by imagining that it is held in the location which the PC points to, here location 105. Counting upwards in hexadecimal towards the destination of the branch should bring the number to 100 on arrival there. Thus we start at 105 containing FC and proceed

104 - FD 103 - FE 102 - FF 101 - 100

Since the destination is 101 the offset is correct. In this example the BNE instruction is a Conditional Branch, in which the branch occurs only if the result of the previous operation was non-zero; otherwise the next instruction starting in location 105 will be executed.

Figure 3.1 Offset calculations for relative addressing.

(e) Indirect Address. In this mode the instruction specifies either a register pair or a store location. The register pair contains the address of the operand; the store location and the location above it contains the 16-bit address of the operand. A register pair used in this way is sometimes called a Data Pointer. Indirect addressing is available in the Z80 and the 6502 and so the specified address in the store contains the low byte of the operand address, and the next location the high byte. In the 8080 the HL register pair was allocated for indirect addressing and this was the only way of accessing the store. The Z80, however, allows either BC or DE to be used, or two store locations.

The 6502 has only one simple indirectly addressed instruction, an indirect jump. This has a two-byte number following the op. code which gives the address of the first (low-order) byte of the operand address. The high byte is held in the next store byte. The 6502 also allows an index register to be used for Indexed Indirect Addressing, or for Indirect Indexed Addressing. In the first of these the contents of the X register are added to the number given in the instruction. This gives the address of the low-order byte of the operand. For example, if the following were the contents of the registers and locations given

| Location   | Contents |

|------------|----------|

| X Register | 28       |

| 48         | 80       |

| 49         | 31       |

| 3180       | 52       |

the instruction LDA (20, X) would be interpreted as follows.

The offset 20 is added to the contents of the index register X to give 48. This is the address of the low byte of the operand (80), and the high byte (31) is held in the next location 49. The two bytes give the 16-bit address 3180 which holds the operand 52. The instruction then loads 52 into the accumulator.

When using Indirect Indexed Addressing the number in the instruction gives the address of the low-order byte Q. The next byte holds the high-order byte P. The contents of the Y register are then added to the 16-bit number PQ to give the address of the operand.

For example, with the following data

| Location   | Contents |  |

|------------|----------|--|

| Register Y | 43       |  |

| 20         | 32 (Q)   |  |

| 21         | 47 (P)   |  |

| 4775       | 6F       |  |

the instruction LDA (20), Y would be interpreted as follows.

The location 20 gives the address of the low byte Q and the address of the high byte P is 21. Two store read operations give the two bytes P and Q which form the 16-bit address 4732. The contents of the Y register are added to this to give 4775, which contains the operand 6F. The final action is to load 6F into the accumulator.

Both of these forms of indirect and indexed addressing allow two parameters of the address to be changed: the register contents and the location held in the store. There is thus scope for quite complicated list seaching and look-up tables.

- (f) Implicit Addressing. This is the mode where the address is indicated in the op. code. It is sometimes called Implied or Inherent Addressing. An example is CLRA (Clear Accumulator A) in the 6800 which requires the single-byte instruction 4F.

- (g) Bit Addressing. This is available in the Z80 and in some single chip microprocessors. It allows a single bit of a specified register to be set, cleared, or tested. For example, the instruction CB 80 will clear bit 0 of register B.

## 3.3 Instruction Types

Microprocessor instructions can be divided broadly into the following types:

- (a) Data transfers. These may be between registers or between a register and a store location.

- (b) Arithmetic operations. These generally take one operand as the initial contents of the accumulator and leave the result also in the accumulator. The other operand may come from an internal register, from the instruction itself, or from the store.

- (c) Logical operations. These are similar to arithmetic operations with regard to the source and destination of the data, but the operations are logical functions performed on each bit of one operand and the corresponding bit of the other operand.

- (d) Incrementing and decrementing. These add one to or subtract one from the contents of an internal register or a store location.

- (e) Shifting and rotating. These operate on a single byte held in either a register or a store location. The rotate operations usually include the carry bit, but the Z80 instructions also allow rotation without the carry.

- (f) Branches. These allow the program to jump out of the normal sequence of instruction execution to some other part of the program if a certain condition is satisfied.

- (g) Stack operations. These can load the stack pointer and transfer data to and from the stack.

- (h) Miscellaneous. These control interrupts, individual flags and include the no operation instruction.

In the following sections instructions will be considered in more detail. A complete specification of all instructions which a particular microprocessor can execute is a complex document, since it must include not only a description of the data handling, but also the number of bytes in the instruction and the number of clock cycles required to fetch and execute it. It is necessary to know which flags may be altered and which are not affected, in order to make proper use of the branch instructions.

### 3.4 Data Transfer Instructions

These are of two types, Load and Store, Load instructions copy the contents of a store location or register into the accumulator or a second register. The data remains in the source, but the old information in the destination is written over and destroyed. When two registers are concerned the destination is usually given first followed by the source. Thus in the Z80 there is a set of instructions such as LD B.C which allows a byte from any 8-bit register to be copied into any other 8-bit register. This instruction copies the contents of C into B. The 6800 allows either accumulator, the stack pointer, or the index register to be loaded with immediate, direct, extended, or indexed addressing. The Z80 also allows any 8-bit register to be loaded with an immediate operand, or from a store location whose address is held in the HL register pair. The accumulator can be loaded as well from an address held in BC or DE. 16 bits can be loaded into either index register (IX or IY), SP, BC, DE, or HL using immediate or absolute addressing. The Z80 also enables the contents of registers to be interchanged; for example EX AF AF' exchanges the contents of the main accumulator and flag register with those of the corresponding alternative set. EXX' performs the same function for the remaining registers B, C, D, E, H and L. There are also block move instructions which use registers HL to hold the source location, DE to hold the destination location, and BC to hold a byte count. When these registers have been loaded, the single instruction LDIR (Load, increment, and repeat) will continue to transfer bytes until the byte counter has reached zero. At each transfer the data pointers HL and DE are incremented and counter BC is decremented. For some applications other actions must be performed on the data between transfers; the instruction LDI (Load and increment) will then effect one data transfer and update the pointers. LDDR and LDD operate in a similar fashion, but work down the store instead of up the store, so that the data pointers are decremented after each transfer.

The 6502 has a single accumulator, two index registers, and a stack pointer which require a byte each and a program counter which holds two bytes. To compensate in part for the lack of extra registers the Accumulator can be loaded with the following address modes:

|            |                                | Op. code   | Op code    |

|------------|--------------------------------|------------|------------|

|            |                                | for LDA    | for STA    |

| (a)        | Immediate                      | <b>A</b> 9 | _          |

| (b)        | Zero page                      | <b>A</b> 5 | 85         |

| (c)        | Absolute                       | AD         | 8D         |

| (d)        | Zero page, indexed with X reg. | <b>B</b> 5 | 95         |

| (e)        | Absolute, indexed with X reg.  | BD         | 9 <b>D</b> |

| <b>(f)</b> | Absolute, indexed with Y reg.  | <b>B</b> 9 | 99         |

| (g)        | Indexed, indirect              | Al         | 81         |

| (h)        | Indirect, indexed              | <b>B</b> 1 | 91         |

The X index register can be loaded with modes (a), (b), (c) and (f), and zero page, indexed with Y. The Y index register can be loaded with modes (a), (b), (c), (d) and (e). The stack pointer can only be loaded via the X register using the TXA instruction which copies the X register into the SP.

The following list gives the op. codes for some typical load instructions:

| 6800     | Address Mode |        |            |          |

|----------|--------------|--------|------------|----------|

| Mnemonic | Immed.       | Direct | Index      | Extended |

| LDAA -   | 86           | 96     | <b>A</b> 6 | В6       |

| LDAB -   | <b>C</b> 6   | D6     | <b>E</b> 6 | F6       |

| LDX -    | CE           | DE     | EE         | FE       |

| LDS -    | BE           | 9E     | ΑE         | BE       |

Here LDX and LDS load the index register and stack pointer.

| <b>Z</b> 80 |        | Addre      | ess Mode |        |      |

|-------------|--------|------------|----------|--------|------|

| Mnemonic    | Immed. | Abs.       | Ind. X   | Ind. Y | (HL) |

| LD A, -     | 3E     | 3 <b>A</b> | DD 7E    | FD 7E  | 7E   |

| LD B, -     | 06     |            | DD 46    | FD 46  | 46   |

| LDC,-       | 0E     |            | DD 4E    | FD 4E  | 4E   |

| LD BC, -    | 01     | ED 48      |          |        |      |

| LD HL, -    | 21     | 2 <b>A</b> |          |        |      |

| LD SP, -    | 31     | ED 7B      |          |        |      |

| LD IX, -    | DD 21  | DD 2A      |          |        |      |

| LD IY, -    | FD 21  | FD 2A      |          |        |      |

|             |        |            |          |        |      |

Store instructions act in a manner similar to Load instructions, but in the reverse direction. One or two bytes from processor registers are copied to some location in the external store, destroying its previous contents. Some confusion is caused because 6800 and 6502 instructions use the word store whereas all Z80 transfers are called Load regardless of the direction of data flow. Since all the microprocessors we are concerned with are what are called 'Single-address' machines, that is they have space for only one address or operand in the instruction, they cannot encode a Store Accumulator instruction with immediate addressing since this would need one byte for the address and a further one for the operand. If we need to load a particular constant into some store location, it must first be loaded into an accumulator or other register and then transferred to the store.

Some typical store instructions are shown in the following table. The code for 6502 instructions is shown above alongside those for the Load instructions.

| 6800     | Address Mode |            |            |

|----------|--------------|------------|------------|

| Mnemonic | Direct       | Index      | Extended   |